# CAT33C104/CAT33C104I

### 4K-Bit SERIAL E2PROM

### **FEATURES**

- Low Power CMOS Technology

- Single 3V Supply

- 256 x 16 or 512 x 8 Selectable Serial Memory

- Self-Timed Write Cycle with Auto-Clear

- Hardware and Software Write Protection

- Power-Up Inadvertant Write Protection

- 100,000 Program/Erase Cycles

- 100 Year Data Retention

- Optional High Endurance Device Available

### DESCRIPTION

The CAT33C104 and CAT33C104I are 4K bit Serial E<sup>2</sup>PROM memory devices which can be configured as either 256 registers by 16 bits (ORG pin at Vcc) or 512 registers by 8 bits (ORG pin at GND). Each register can be written (or read) serially by using the DI (or DO) pin. The CAT33C104/CAT33C104I is manufactured using Catalyst's advanced CMOS E<sup>2</sup>PROM floating gate technology. It is designed to endure 100,000 program/erase cycles and has a data retention of 100 years. The device is available in 8 pin DIP or SO packages.

### PIN CONFIGURATION

| DIP Pa                        | nckage                           | SO Pac                                | kage S                                  | SO Pac                                | kage K       |

|-------------------------------|----------------------------------|---------------------------------------|-----------------------------------------|---------------------------------------|--------------|

| CS -1<br>SK 2<br>DI 3<br>DO 4 | 8  VCC<br>7 NC<br>6 ORG<br>5 OND | CS [ •1<br>SK [ 2<br>DI [ 3<br>DO [ 4 | 8 7 VCC<br>7 7 NC<br>6 7 ORG<br>5 7 GND | CS [ •1<br>SK [ 2<br>D] [ 3<br>DO [ 4 | 8            |

|                               |                                  |                                       |                                         |                                       | 5047 FHD F01 |

# **PIN FUNCTIONS**

| Pin Name | Function            |  |  |  |  |

|----------|---------------------|--|--|--|--|

| cs       | Chip Select         |  |  |  |  |

| SK       | Clock Input         |  |  |  |  |

| DI       | Serial Data Input   |  |  |  |  |

| DO       | Serial Data Output  |  |  |  |  |

| Vcc      | +3V Power Supply    |  |  |  |  |

| GND      | Ground              |  |  |  |  |

| NC       | No Connection       |  |  |  |  |

| ORG      | Memory Organization |  |  |  |  |

Note: When the ORG pin is connected to V<sub>CC</sub>, the 256 x 16 organization is selected. When it is connected to ground, the 512 x 8 organization is selected. If the ORG pin is left unconnected, then an internal pullup device will select the 256 x 16 organization.

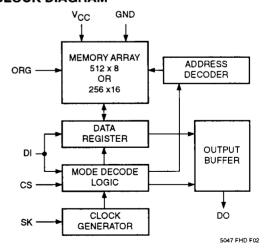

### **BLOCK DIAGRAM**

TD 5047

### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias55°C to +125°C                                                       |

|--------------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                          |

| Voltage on any Pin with<br>Respect to Ground <sup>(1)</sup> 2.0V to +V <sub>CC</sub> +2.0V |

| V <sub>CC</sub> with Respect to Ground2.0V to +7.0V                                        |

| Package Power Dissipation Capability (Ta = 25°C)1.0W                                       |

| Lead Soldering Temperature (10 secs)300°C                                                  |

| Output Short Circuit Current <sup>(2)</sup> 100 mA                                         |

### \*COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

### RELIABILITY CHARACTERISTICS

| Symbol                         | Parameter          | Min.    | Max. | Units       | Reference Test Method         |

|--------------------------------|--------------------|---------|------|-------------|-------------------------------|

| N <sub>END</sub> (3)           | Endurance          | 100,000 |      | Cycles/Byte | MIL-STD-883, Test Method 1033 |

| T <sub>DR</sub> <sup>(3)</sup> | Data Retention     | 100     |      | Years       | MIL-STD-883, Test Method 1008 |

| V <sub>ZAP</sub> (3)           | ESD Susceptibility | 2000    |      | Volts       | MIL-STD-883, Test Method 3015 |

| I <sub>LTH</sub> (3)(4)        | Latch-Up           | 100     |      | mA          | JEDEC Standard 17             |

### D.C. OPERATING CHARACTERISTICS

CAT33C104  $T_A$ = 0°C to +70°C,  $V_{CC}$  = +3V±10%, unless otherwise specified. CAT33C104I  $T_A$ = -40°C to +85°C,  $V_{CC}$  = +3V±10%, unless otherwise specified.

|                  |                                            |                       |           | ·       | ,     |                                                                           |

|------------------|--------------------------------------------|-----------------------|-----------|---------|-------|---------------------------------------------------------------------------|

|                  |                                            |                       | Limits    |         |       |                                                                           |

| Symbol           | Parameter                                  | Min.                  | Min. Typ. |         | Units | Test Conditions                                                           |

| lcc <sub>1</sub> | Power Supply Current (Operating)           |                       |           | 2       | mA    | DI = 0.0V, SK = 3.0V<br>V <sub>CC</sub> = 3.0V, CS = 3.0V,<br>Output Open |

| lcc2             | Power Supply Current (Standby)             |                       |           | 50      | μА    | V <sub>CC</sub> = 3.3V, CS = 0V<br>DI = 0V SK = 0V                        |

| lu lu            | Input Leakage Current                      |                       |           | 2       | μА    | V <sub>IN</sub> = 0V to 3.3V                                              |

| llo              | Output Leakage Current (Including ORG Pin) |                       |           | 10      | μΑ    | V <sub>OUT</sub> = 0V to 3.3V,<br>CS = 0V                                 |

| V <sub>IH</sub>  | High Level Input Voltage                   | V <sub>CC</sub> - 0.3 |           | Vcc + 1 | V     |                                                                           |

| V <sub>IL</sub>  | Low Level Input Voltage                    | -0.1                  |           | 0.3     | V     |                                                                           |

| V <sub>OH</sub>  | High Level Output Voltage                  | V <sub>CC</sub> - 0.3 |           |         | V     | loн = −10µA                                                               |

| V <sub>OL</sub>  | Low Level Output Voltage                   |                       |           | 0.3     | V     | I <sub>OL</sub> = 10μA                                                    |

#### Note:

<sup>(1)</sup> The minimum DC input voltage is -0.5V. During transitions, inputs may undershoot to -2.0V for periods of less than 20 ns. Maximum DC voltage on output pins is V<sub>CC</sub> +0.5V, which may overshoot to V<sub>CC</sub> +2.0V for periods of less than 20 ns.

<sup>(2)</sup> Output shorted for no more than one second. No more than one output shorted at a time.

<sup>(3)</sup> This parameter is tested initially and after a design or process change that affects the parameter.

<sup>(4)</sup> Latch-up protection is provided for stresses up to 100 mA on address and data pins from -1V to V<sub>CC</sub> +1V.

# **INSTRUCTION SET**

|                     | Start Bit | Opcode | Address   |          | Data    |          |                     |

|---------------------|-----------|--------|-----------|----------|---------|----------|---------------------|

| Instruction         |           |        | 512 x 8   | 256 x 16 | 512 x 8 | 256 x 16 | Comments            |

| READ                | 1         | 10     | A8-A0     | A7–A0    |         |          | Read Address AN-A0  |

| ERASE               | 1         | 11     | A8-A0     | A7-A0    |         |          | Clear Address AN-A0 |

| WRITE               | 1         | 0 1    | A8-A0     | A7-A0    | D7-D0   | D15D0    | Write Address AN-A0 |

| EWEN                | 1         | 0 0    | 11XXXXXXX | 11XXXXXX |         |          | Write Enable        |

| EWDS                | 1         | 0 0    | 00XXXXXXX | 00XXXXXX |         |          | Write Disable       |

| ERAL                | 1         | 0 0    | 10XXXXXXX | 10XXXXXX |         |          | Clear All Addresses |

| WRAL <sup>(5)</sup> | 1         | 0 0    | 01XXXXXXX | 01XXXXXX | D7-D0   | D15-D0   | Write All Addresses |

### A.C. CHARACTERISTICS

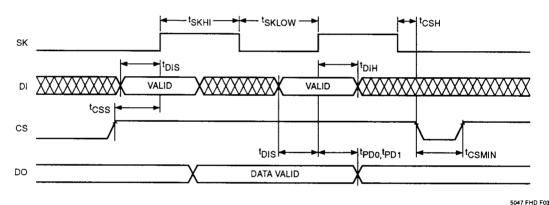

CAT33C104 T<sub>A</sub>= 0°C to +70°C, V<sub>CC</sub> = +3V $\pm$ 10%, unless otherwise specified. CAT33C104I T<sub>A</sub>= -40°C to +85°C, V<sub>CC</sub> = +3V $\pm$ 10%, unless otherwise specified.

|                     |                              |      | Limits |      |       |                         |

|---------------------|------------------------------|------|--------|------|-------|-------------------------|

| Symbol              | Parameter                    | Min. | Тур.   | Max. | Units | <b>Test Conditions</b>  |

| toss                | CS Setup Time                | 200  |        |      | ns    |                         |

| tсsн                | CS Hold Time                 | 0    |        |      | ns    | C <sub>L</sub> = 100pF  |

| t <sub>DIS</sub>    | DI Setup Time                | 400  |        |      | ns    | $V_{OL} = 0.3V$         |

| tDIH                | DI Hold Time                 | 400  |        |      | ns    | $V_{OH} = V_{CC} - 0.3$ |

| t <sub>PD1</sub>    | Output Delay to 1            |      |        | 2    | μs    | $V_{IL} = 0.3V$         |

| t <sub>PD0</sub>    | Output Delay to 0            |      |        | 2    | μs    | $V_{IH} = V_{CC} - 0.3$ |

| t <sub>HZ</sub> (3) | Output Delay to High-Z       |      |        | 400  | ns    |                         |

| t <sub>EW</sub>     | Program/Erase Pulse Width    |      |        | 20   | ms    |                         |

| tcsmin              | Minimum CS Low Time          | 1    |        |      | μs    |                         |

| tskHI               | Minimum SK High Time         | 1    |        |      | μs    |                         |

| tskLow              | Minimum SK Low time          | 1    |        |      | μs    |                         |

| tsv                 | Output Delay to Status Valid |      |        | 1    | μѕ    | C <sub>L</sub> = 100pF  |

| SK <sub>MAX</sub>   | Maximum Clock Frequency      | DC   |        | 250  | kHz   |                         |

### Note:

<sup>(3)</sup> This parameter is tested initially and after a design or process change that affects the parameter.

<sup>(5)</sup> The WRAL command is for test mode only and is not guaranteed over operating conditions.

### **DEVICE OPERATION**

The CAT33C104/CAT33C104I is a 4096 bit nonvolatile memory intended for use with industry standard microprocessors. The CAT33C104/CAT33C104I can be organized as either 256 registers by 16 bits, or as 512 registers by 8 bits. Seven 11 bit instructions (12 bit instruction in 512 by 8 organization) control the reading, writing and erase operations of the device. The CAT33C104/CAT33C104I operates on a single 3V supply and will generate on chip, the high voltage required during any write operation.

Instructions, addresses, and write data are clocked into the DI pin on the rising edge of the clock (SK). The DO pin is normally in a high impedance state except when reading data from the device, or when checking the ready/busy status after a write operation.

The ready/busy status can be determined after a write

operation by selecting the device (CS high) and polling the DO pin; DO low indicates that the write operation is not completed, while DO high indicates that the device is ready for the next instruction. If necessary, the DO pin may be placed back into a high impedance state during chip select by shifting a dummy "1" into the DI pin. The DO pin will enter the high impedance state on the falling edge of the clock (SK). Placing the DO pin into the high impedance state is recommended in applications where the DI pin and the DO pin are to be tied together to form a common DI/O pin.

The format for all instructions sent to the CAT33C104/CAT33C104l is a logical "1" start bit, a 2 bit (or 4 bit) op code, a 8 bit address (9 bit address when organized as 512 x 8), and for write operations a 16 bit data field (8 bit data field when organized as 512 x 8).

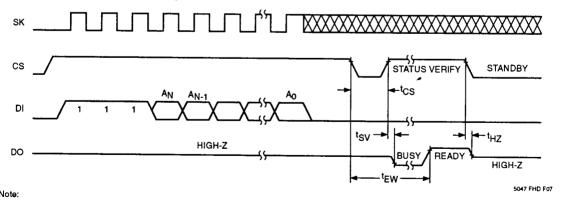

Figure 1. Sychronous Data Timing (6)

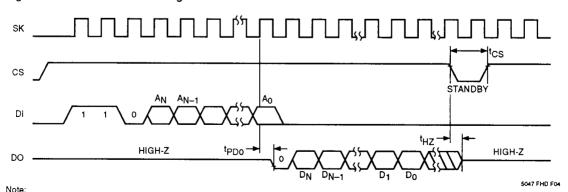

Figure 2. Read Instruction Timing (6)

(6) The ORG pin is used to configure the device for x8 or x16 operation. When x8 organization is selected, AN = A8 and DN = D7. When x16 organization is selected, AN = A7 and DN = D15.

At power-down, when  $V_{CC}$  falls below a threshold of approximately 2.4V, the data protection circuitry inhibits the erase and write instructions and a write disable (EWDS) is executed internally.

#### Read

Upon receiving a READ command and an address (clocked into the DI pin), the DO pin of the CAT33C104/CAT33C104I will come out of the high impedance state and, after sending an initial dummy zero bit, will begin shifting out the data addressed. The output data bits will toggle on the rising edge of the SK clock and are stable after the specified time delay (tepo or teps).

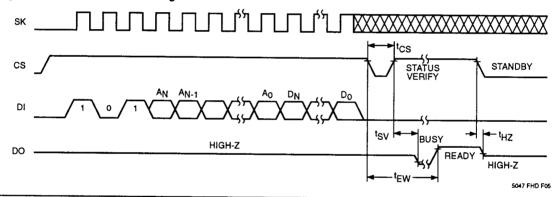

### Write

After receiving a WRITE command, address and the data, the CS (chip select) pin must be deselected for a

minimum of 1µs (tcsmin). The falling edge of CS will start the self clocking clear and data store cycle of the memory location specified in the instruction. The clocking of the SK pin is not necessary after the device has entered the self clocking mode. The ready/busy status of the CAT33C104/CAT33C104I can be determined by selecting the device and polling the DO pin. Since this device features Auto-Clear before write, it is NOT necessary to erase a memory location before the WRITE command is sent.

#### Erase

Upon receiving an ERASE command and address, the CS (chip select) pin must be deselected for a minimum of 1µs (tcsmin). The falling edge of CS will start the self clocking clear cycle of the memory location specified in the instruction. The clocking of the SK pin is not neces-

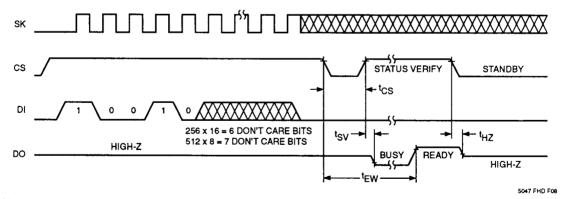

Figure 3. Write Instruction Timing (6)

Figure 4. Erase Instruction Timing (6)

(6) The ORG pin is used to configure the device for x8 or x16 operation. When x8 organization is selected, AN = A8 and DN = D7. When x16 organization is selected, AN = A7 and DN = D15.

sary after the device has entered the self clocking mode. The ready/busy status of the CAT33C104/CAT33C104l can be determined by selecting the device and polling the DO pin. Once cleared, the content of a cleared location returns to a logical "1" state.

### Erase/Write Enable and Disable

The CAT33C104/CAT33C104I powers up in the write disable state. Any writing after power-up or after an EWDS (write disable) instruction must first be preceded by the EWEN (write enable) instruction. Once the write instruction is enabled, it will remain enabled until power to the device is removed, or the EWDS instruction is sent. The EWDS instruction can be used to disable all CAT33C104/CAT33C104I write and clear instructions.

and will prevent any accidental writing or clearing of the device. Data can be read normally from the device regardless of the write enable/disable status.

#### Erase All

Upon receiving an ERAL command, the CS (chip select) pin must be deselected for a minimum of 1µs (tcsmin). The falling edge of CS will start the self clocking clear cycle of all memory locations in the device. The clocking of the SK pin is not necessary after the device has entered the self clocking mode. The ready/busy status of the CAT33C104/CAT33C104I can be determined by selecting the device and polling the DO pin. Once cleared, the contents of all memory bits return to a logical "1" state.

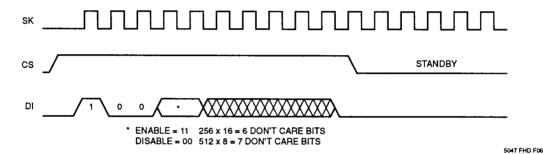

Figure 5. EWEN/EWDS Instruction Timing (6)

Figure 6. ERAL Instruction Timing (6)

Note:

<sup>(6)</sup> The ORG pin is used to configure the device for x8 or x16 operation. When x8 organization is selected, AN = A8 and DN = D7. When x16 organization is selected, AN = A7 and DN = D15.

### Write All

Upon receiving a WRAL command and data, the CS (chip select) pin must be deselected for a minimum of 1µs (tcsmin). The falling edge of CS will start the self clocking data write to all memory locations in the device.

The clocking of the SK pin is not necessary after the device has entered the self clocking mode. The ready/ busy status of the CAT33C104/CAT33C104I can be determined by selecting the device and polling the DO pin. It IS NOT necessary for all memory locations to be cleared before the WRAL command is executed.

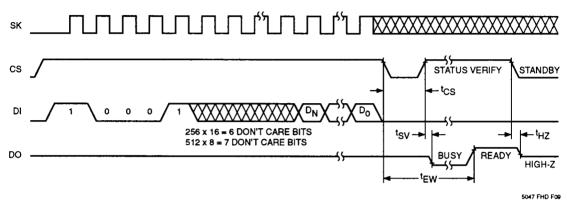

Figure 7. WRAL Instruction Timing (6)

#### Note:

(6) The ORG pin is used to configure the device for x8 or x16 operation. When x8 organization is selected, AN = A8 and DN = D7. When x16 organization is selected, AN = A7 and DN = D15.