82530 82\$31

DIGITAL 8000 SERIES SCHOTTKY TTL/MSI 82532

# ESCRIPTION

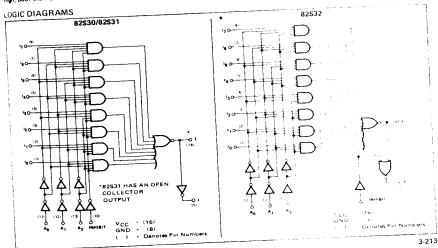

use 8-Input Digital Multiplexers are the logical equivalent a single-pole, 8 position switch whose position is specid by a 3-bit input address.

he 82S30 incorporates an INHIBIT input which, when w, allows the one-of-eight inputs selected by the address p appear on the f output and, in complement, on the f utput. With the INHIBIT input high, the f output is unonditionally low and the f output is unconditionally high. the 82S31 is a variation of the 82S30 that provides an pen collector output f for expansion of input terms.

The B2S32 is similar to the B2S30 except in the effect of the INHIBIT input on the f output. With the INHIBIT low, the selected input appears at the f output and, in complement, on the f output. With the INHIBIT input high, both the f and the f output are unconditionally low.

## FEATURES

- SCHOTTKY-CLAMPED TTL STRUCTURE

- LOW CURRENT PNP INPUTS

- 82S30 REPLACES 9312 FOR HIGHER SPEED

- 82S31 HAS OPEN COLLECTOR OUTPUT

- 82S32 HAS DIRECT OUTPUT IHNIBIT

# D.C. ELECTRICAL CHARACTERISTICS Over Recommended Operating Temperat

| CHARACTERISTICS                                    | LIMITS     |     |              |       |                | TEST CONDITIONS |           |           |            |         |      |  |

|----------------------------------------------------|------------|-----|--------------|-------|----------------|-----------------|-----------|-----------|------------|---------|------|--|

|                                                    | MIN        | TYP | MAX          | UNITS | A <sub>1</sub> | A <sub>2</sub>  | А3        | INH       | DATA INPUT | OUTPUTS | NOTE |  |

| "I" Output Voltage (All outputs except f of 82S31) | 2.7        |     |              | ٧     |                |                 |           |           |            | -1.0mA  | 6,10 |  |

| "I" Output Leakage Current "O" Output Voltage      | 1 1        |     | 250          | μΑ    |                |                 |           |           |            | '       |      |  |

| "I" Input Current                                  | ] [        |     | 0.5          | V     | •              |                 |           | ١.        |            | 20mA    | 7.10 |  |

| Inputs An, In, Inh "O" Input Current               |            |     | 10           | μА    | 4.5V           | 4.5∨            | 4.5∨      | 4.5∨      | 4.5V       |         |      |  |

| An, In, INH<br>Power Consumption/                  |            | İ   | -400         | μΑ    | 0.5∨           | 0.5∨            | 0.5∨      | 0.5∨      | 0.5V       |         |      |  |

| Supply Current Output Short Circuit Current        |            |     | 325/62       | nW/m∆ | 4.5V           | 4.5V            | 4.5∨      | 4.5∨      | 0∨         |         | 9,11 |  |

| Output <u>f</u><br>Output <del>f</del>             | -40<br>-40 | - 1 | -100<br>-100 |       | 0V<br>0V       | 0V<br>0V        | 0٧        | ov        | 4.5V       | ov      | 9    |  |

| Input Clamp Voltage                                | -1.2       |     |              | V     | -18            | -18             | 0V<br>-18 | 0V<br>-18 | 0V         | ov      | 9    |  |

| e Truth Table for logical conditions.              | <u>.</u>   | L   |              | i     | mA             | mA              | mA        | mA        |            | i i     |      |  |

# A.C. ELECTRICAL CHARACTERISTICS T<sub>A</sub> = 25°C and $V_{CC}$ = 5.0V

| CHARACTERISTICS                                                                                                                         |                                                                                                     | L   | LI                            | MITS                                  | 1                                |                                               |   |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----|-------------------------------|---------------------------------------|----------------------------------|-----------------------------------------------|---|--|

|                                                                                                                                         | MIN                                                                                                 | TYP | MAX                           | UNITS                                 | TEST CONDITIONS                  | NOTES                                         |   |  |

| Propagation Delay (Data, $I_n$ to $\overline{f}$ Address $A_n$ to $\overline{f}$ $\overline{f}$ to $\overline{f}$ INH to $\overline{f}$ | (t <sub>on</sub> ,t <sub>off</sub> )<br>82530/32<br>82531<br>82530/32<br>82531<br>82530/32<br>82531 |     | 7<br>9<br>14<br>16<br>6<br>12 | 10<br>12<br>17<br>19<br>9<br>16<br>18 | ns<br>ns<br>ns<br>ns<br>ns<br>ns | Per Test Table $R_L = 280\Omega$ $C_L = 15pF$ | 8 |  |

#### NOTES

- 1. All voltage measurements are referenced to the ground terminal. Terminals not specifically referenced are left electrically open.

- 2. All measurements are taken with ground pin tied to zero volts.

- 3. Positive current is defined as into the terminal referenced.

- 4. Positive logic definition: "UP" Level = "1", "DOWN" Level = "0".

- 5. Precautionary measures should be taken to ensure current limiting in accordance with Absolute Maximum Ratings. 6. Output source current is supplied through a resistor to ground.

- 7. Output sink current is supplied through a resistor to VCC-

- 8. Refer to AC Test Figures.

- 9. V<sub>CC</sub> = 5.25V.

- 10. By DC tests per the truth table, all inputs have guaranteed thresholds at 0.8V for logical "0" and 2.0V for logical "1".

- 3-214

# TRUTH TABLE

|                |        |                | I  |    |    |     |      |       |    |    | 1   | OUTPUTS |                       |       |  |

|----------------|--------|----------------|----|----|----|-----|------|-------|----|----|-----|---------|-----------------------|-------|--|

|                | ADDRES | SS             | ŀ  |    |    | - 1 | DATA | INPUT |    |    |     |         | f                     | -     |  |

| A <sub>2</sub> | A1     | A <sub>0</sub> | 17 | 16 | 15 | 14  | 13   | 12    | )1 | 10 | INH | t       | 8253 <b>0</b> /<br>31 | 82832 |  |

| 0              | 0      | 0              | ×  | ×  | ×  | ×   | ×    | ×     | ×  | 1  | 0   | 1       | 0                     | 0     |  |

| 0              | 0      | 1              | ×  | ×  | ×  | ×   | ×    | ×     | 1  | ×  | 0   | : 1     | 0                     | 0     |  |

| 0              | 1      | 0              | ×  | ×  | ×  | ×   | Х    | 1     | ×  | ×  | 0   | 1       | 0                     | 0     |  |

| 0              | 1      | 1              | ×  | ×  | x  | х   | 1    | х     | ×  | Х  | O   | 1       | 0                     | 0     |  |

| 1              | 0      | 0              | ×  | ×  | ×  | 1   | х    | х     | ×  | ×  | 0   | 1       | 0                     | 0     |  |

| 1              | 0      | 1              | x  | ×  | 1  | ×   | x    | х     | ×  | ×  | 0   | 1       | 0                     | 0     |  |

| 1              | 1      | 0              | ×  | 1  | ×  | ×   | x    | ×     | ×  | х  | 0   | 1       | 0                     | 0     |  |

| 1              | 1      | 1              | 1  | ×  | ×  | ×   | ×    | ×     | ×  | ×  | 0   | 1       | 0                     | 0     |  |

| 0              | 0      | 0              | ×  | х  | ×  | х   | Х    | х     | ×  | 0  | 0   | 0       | 1                     | 1     |  |

| 0              | 0      | 1              | ×  | x  | x  | х   | ×    | ×     | 0  | ×  | 0   | Ü       | 1                     | 1     |  |

| 0              | 1      | 0              | С  | ×  | x  | x   | ×    | 0     | ×  | х  | 0   | 0       | 1                     | 1     |  |

| 0              | 1      | 1              | ×  | ×  | x  | х   | 0    | ×     | ×  | ×  | 0   | 0       | 1                     | 1     |  |

| 1              | 0      | 0              | ×  | ×  | ×  | 0   | ×    | x     | х  | ×  | 0   | 0       | 1                     | 1     |  |

| 1              | 0      | 1              | x  | х  | 0  | х   | ×    | x     | ×  | ×  | 0   | 0       | 1                     | 1     |  |

| 1              | 1      | 0              | ×  | 0  | ×  | ×   | ×    | ×     | ×  | ×  | 0   | 0       | 1                     | 1     |  |

| 1              | 1      | 1              | 0  | ×  | ×  | ×   | ×    | ×     | ×  | ×  | 0   | 0       | 1                     | 1     |  |

| X              | ×      | ×              | С  | ×  | ×  | ×   | ×    | х     | ×  | ×  | 1   | 0       | 1                     | 0     |  |

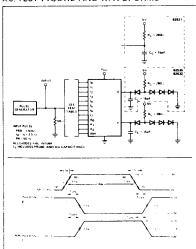

### A.C. TEST FIGURE AND WAVEFORMS

### TEST TABLE

| TEST |    |                |                |     | INI | ٠U | rs |    |    | OUTPUTS |    |    |   |   |

|------|----|----------------|----------------|-----|-----|----|----|----|----|---------|----|----|---|---|

| NO.  | Αo | A <sub>1</sub> | A <sub>2</sub> | INH | 10  | 11 | 12 | 13 | 14 | 15      | 16 | 17 | F | F |

| 1    | PG | 0              | 0              | 0   | 0   | 1  | 0  | 0  | 0  | 0       | 0  | 0  | Т | Т |

| 2    | 0  | PG             | 0              | 0   | 0   | 0  | 1  | 0  | 0  | 0       | 0  | 0  | Т |   |

| 3    | 0  | 0              | PG             | 0   | 0   | 0  | 0  | 0  | 1  | 0       | 0  | 0  | T |   |

| 4    | 0  | 1              | 1              | PG  | 0   | 0  | 0  | 0  | 0  | 1       | 0  | 0  | T |   |

| 5    | 1  | 1              | 1              | 0   | 0   | 0  | 0  | 0  | 0  | 0       | 0  | PG | T |   |

F. "I" = 2 7V '0" - GROUND

AC test jigs must have less than 1.8 inchilead lengths from package pins.

3-215