## **FEATURES**

#### ■ Integrated single-chip solution

- Compatible with IBM<sup>®</sup> VGA hardware

- Programmable frequency synthesizer

- RAMDAC

- Frame accelerator for less power consumption

#### ■ Direct connection to host bus

- 32-bit '486 local bus

- VESA<sup>®</sup> VL-Bus™

- 16-bit '386 local bus

- ISA bus (PC AT)

### ■ Supports a variety of 640 × 480 LCDs

- Dual- and single-scan color STN

- Dual- and single-scan monochrome STN

- 9-, 12-, and 18-bit color TFT

- Multi-shade monochrome TFT

- Simultaneous CRT and LCD operation (SimulSCAN™) in 640 × 480 256-color modes for all supported LCDs, including dual-scan color STN LCDs

- Up to 64 shades (at 640 × 480) with monochrome STN and TFT LCDs

- CRT resolution up to  $1024 \times 768$  with 16 colors or  $800 \times 600$  with 256 colors

- Maximum 65-MHz video clock at 5.0 V

- Maximum 40-MHz video clock at 3.3 V

- 132-column text modes

# Subnotebook LCD VGA Controller

#### ■ Windows® performance-improvement features

- True packed-pixel addressing

- Color expansion for 8-bit-per-pixel graphics

- 32 × 32 hardware graphics cursor (2 bits per pixel)

- Improved data latches for block moves

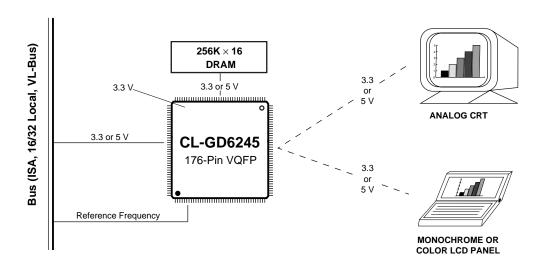

## ■ Supports single 256K × 16 DRAM configuration

- Symmetric or asymmetric DRAMs

- Dual-WE\* or dual-CAS\* DRAMs

- Self-refresh DRAMs

- Maximum 50-MHz memory clock at 5.0 V

- Maximum 45-MHz memory clock at 3.3 V

#### ■ Supports 3.3- and 5.0-V mixed-voltage operation

- Standby and Suspend modes for reduced power consumption

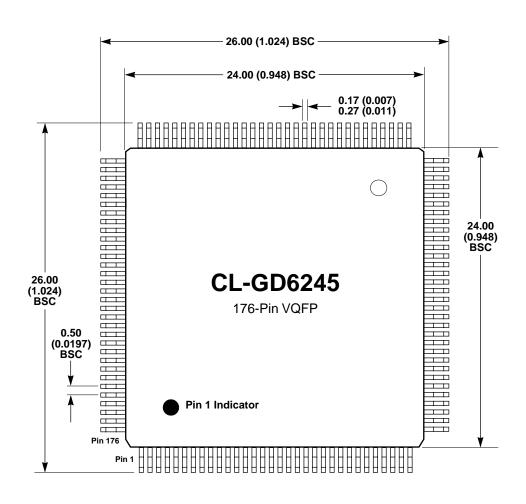

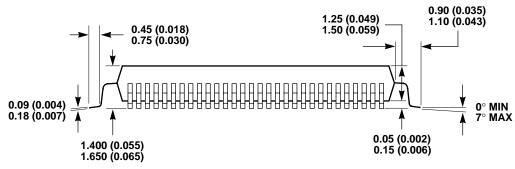

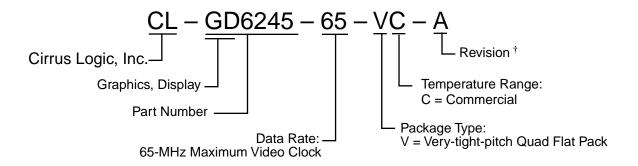

- 176-pin (EIAJ standard) VQFP package

- Small form factor

- Thin 1.4-mm package

#### **OVERVIEW**

The CL-GD6245 is an advanced, single-chip, VGA LCD controller that is optimized for low-cost note-book and subnotebook personal computers with stringent form-factor, display-quality, and power-consumption requirements.

The CL-GD6245 integrates the RAMDAC, frequency synthesizer, color/monochrome STN/TFT LCD interface, LCD power-sequencing logic, host bus interface, and all other functional logic necessary to operate a VGA-compatible video subsystem. This video subsystem is completed with the addition of a single 256K × 16 DRAM. To further minimize board space, the CL GD6245 is packaged in a 176-pin VQFP package, which also features a minimized height for use on boards with two-sided component assembly.

## LCD, VGA, or SimulSCAN™

The CL-GD6245 supports  $640 \times 480$  dual-/single-scan color/monochrome STN LCDs and color/monochrome TFT LCDs.

The CL-GD6245 provides up to 64 gray shades or 262,144 (256K) colors on STN LCDs. A state-of-the-art grayscaling algorithm significantly reduces flicker and pattern motion in gray shades with the latest fast-response STN LCDs. The CL-GD6245 provides a 9-, 12-, or 18-bit interface to TFT LCDs. CRTs with resolutions up to  $1024 \times 768$  with 16 colors or  $800 \times 600$  with 256 colors are supported.

The CL-GD6245 provides simultaneous CRT and LCD operation (SimulSCAN™) for single- and dual-scan color and monochrome LCDs, as well as fixed- and multi-frequency analog CRTs. Using a single DRAM for display memory, the CL-GD6245 optimizes the memory and LCD interfaces to provide  $640 \times 480$  256-color SimulSCAN operation on dual-scan color STN LCDs.

### **Direct Host Bus Connection**

The host interface of the CL-GD6245 is designed for use with various CPUs, including direct connection to 32-bit '486 local bus, VESA® VL-Bus™, and ISA bus. Moreover, most popular core-logic chip sets can be directly connected to the CL-GD6245

without additional components. The '486 burst mode for multiple-cycle accesses is also supported to further enhance graphics performance.

## High Performance and Low Power

The CL GD6245's integrated frame-accelerator technology enables low-power LCD operation with high LCD vertical-refresh rates. The CL-GD6245 efficiently uses the unused portions of display memory for the frame accelerator so additional DRAMs are not required.

The CL-GD6245 combines high performance with design flexibility in CPU, display-memory interface, and power management. The CL-GD6245 offers true packed-pixel addressing, color expansion for 8-bit-per-pixel graphics, and a hardware graphics cursor, thus improving Windows® performance. Other incorporated features that boost performance include memory-write buffers and internal asynchronous display-data FIFOs.

Each interface on the CL-GD6245 can operate from either a 3.3- or 5.0-V power supply. Mixed-voltage operation is optimized for quick implementation of a notebook computer with reduced power consumption. The display memory, host bus interface, LCD interface, and CRT interface can be independently implemented for either 3.3 or 5.0 V, in any combination.

Standby and Suspend power-management modes reduce power consumption when the system is not active. The internal Standby Counter can initiate Standby mode without software intervention. During this reduced-power mode, the LCD is turned off, while the display memory can be accessed and modified. In Suspend mode, all I/O pins, except a dedicated Suspend-mode pin, are deactivated to further reduce power consumption. In this mode, the display-memory data is preserved but cannot be accessed — this feature is useful when a system remains inactive for a relatively long time.

# **Table of Contents**

| 1.           | PIN INFORMATION                                                 | 5   | 3.6.1  | '486 Burst Mode Support                                         | 37 |

|--------------|-----------------------------------------------------------------|-----|--------|-----------------------------------------------------------------|----|

| 1.1          | Pin Diagram                                                     | 5   | 3.6.2  | Address Decoding and Latching                                   | 37 |

| 1.2          | Dual-Scan STN Color Panel Connections —                         |     | 3.6.3  | Bus Cycle Restart                                               | 37 |

|              | '486DX Local Bus Using 256K × 16 DRAM                           |     | 3.6.4  | Other Bus Considerations                                        | 37 |

|              | with Dual CAS*                                                  | 6   | 3.7    | LCD Flat-Panel Interface                                        | 38 |

| 1.3          | TFT Color Panel Connections — '386SX                            |     | 3.7.1  | LCD Resolution Compensation for 640 × 480                       |    |

|              | Local Bus Using 256K × 16 DRAM with Dual WE*                    | 7   |        | LCDs                                                            |    |

| 1.4          | TFT Color Panel Connections — '386DX                            | /   | 3.7.2  | Frame Rate Modulation                                           |    |

| 17           | Local Bus Using 256K × 16 DRAM with Dual                        |     | 3.7.3  | Dithering Engine                                                |    |

|              | WE*                                                             | 8   | 3.8    | Power Management and Sequencing                                 |    |

| 1.5          | Typical Dual-Scan Monochrome Panel                              |     | 3.8.1  | Normal Mode                                                     |    |

|              | Connections — ISA Bus Using 256K × 16                           |     | 3.8.2  | Power-Management Pins                                           | 42 |

|              | DRAM with Dual CAS*                                             |     | 3.8.3  | Standby Mode                                                    | 42 |

| 1.6          | Pin Summary                                                     | .10 | 3.8.4  | Suspend Mode                                                    | 43 |

| 2.           | DETAILED PIN DESCRIPTIONS                                       | 15  | 3.8.5  | Power Sequencing                                                |    |

| 2.1          | Host Interface Pins                                             | .15 | 3.8.6  | Additional Power Management Features                            |    |

| 2.1.1        | ISA-Bus-Mode Host Interface Pins                                | .16 |        | Analog Outputs                                                  |    |

| 2.1.2        | Local-Bus-Mode Host Interface Pins                              | .21 |        | Color Lookup Table                                              |    |

| 2.2          | CRT Interface Pins                                              |     | 3.10.1 | 9                                                               |    |

| 2.3          | LCD Flat-Panel Interface Pins                                   |     | 3.10.2 | Reading from the Color Lookup Table                             | 45 |

| 2.3.1        | General Flat-Panel Interface Pins                               |     | 4.     | <b>CL-GD6245 VIDEO MODE TABLES</b>                              | 46 |

| 2.3.2        | Monochrome Flat-Panel Interface Pins                            |     | 4.1    | CRT Video Modes                                                 | 46 |

| 2.3.3        | STN Color Flat-Panel Interface Pins                             |     | 4.2    | LCD Flat-Panel Video Modes                                      | 48 |

| 2.3.4        | TFT Color Flat-Panel Interface Pins                             |     | 5.     | VGA REGISTER PORT MAP                                           | 49 |

| 2.4          | Display Memory Interface Pins                                   |     | _      |                                                                 |    |

| 2.5          | Miscellaneous Pins                                              |     |        | REGISTER INFORMATION                                            |    |

| 2.6          | Power Management Pins                                           |     | 6.1    | Register Summary Tables                                         |    |

| 2.7<br>2.8   | Dual-Frequency Synthesizer Interface Pins Power and Ground Pins |     | 6.2    | Extended External/General and VGA Graphics Controller Registers |    |

|              |                                                                 |     | 6.2.1  | STAT: Input Status Register 1                                   |    |

| 3.           | FUNCTIONAL DESCRIPTION                                          |     | 6.2.2  | GR0: Set/Reset (CL-GD6245 Extensions)                           |    |

| 3.1          | General                                                         |     | 6.2.3  | GR1: Set/Reset Enable (CL-GD6245                                | 50 |

| 3.2          | Functional Blocks                                               |     | 0.2.3  | Extensions)                                                     | 57 |

| 3.2.1        | CPU Interface                                                   |     | 6.2.4  | GR5: Mode (CL-GD6245 Extensions)                                |    |

| 3.2.2        | Graphics Controller                                             |     |        | CL-GD6245 Extension Registers                                   |    |

| 3.2.3        | Display-Memory Interface                                        |     | 6.3.1  | · · · · · · · · · · · · · · · · · · ·                           |    |

| 3.2.4        | Graphics Interface                                              |     | 6.3.2  | SR7: Extended Sequencer Modes                                   |    |

| 3.2.5        | Dual-Frequency Clock Synthesizer                                |     | 6.3.3  | SR8: Miscellaneous Control 1                                    |    |

| 3.3          | Functional Operation                                            |     | 6.3.4  | SR9, SRA, SR14, SR15, SR19: Scratchpad                          |    |

| 3.3.1        | CPU Access to Registers                                         |     |        | [0, 1, 2, 3, 4]                                                 | 63 |

| 3.3.2        | CPU Access to Display Memory                                    |     | 6.3.5  | SRB, SRC, SRD, SRE: VCLK[0, 1, 2, 3]                            |    |

| 3.3.3        | Display-Memory Refresh                                          |     |        | Numerator Value                                                 |    |

| 3.3.4<br>3.4 | Screen RefreshPerformance                                       |     | 6.3.6  | SRF: DRAM Control                                               | 66 |

| 3.4<br>3.5   | Compatibility                                                   |     | 6.3.7  | SR10, SR30, SR50, SR70, SR90, SRB0,                             |    |

| 3.6          | Bus Interface                                                   |     |        | SRD0, SRF0: Graphics Cursor X Position                          | 00 |

| 5.5          | שמט ווונטוומטט ווונטוומטט ווונטוומטט ווונטוומטט                 | .01 |        | [0-7]                                                           | 80 |

| 6.3.12<br>6.3.13 | SR1A: Dual-Scan Color Control                   | 6.4.7  | (MISC[7:6] = '00')<br>CR6X: LFS Vertical Counter Value Compa |      |

|------------------|-------------------------------------------------|--------|--------------------------------------------------------------|------|

|                  | Denominator and Post-scalar Values74            |        | Overflow                                                     | 105  |

| 6.3.14           | SR1F: Memory Clock Frequency Programming76      | 6.4.8  | CR7X: Panel Signal Control for Color TFT Panels              | 106  |

| 6.3.15           | GR9: Offset 077                                 | 6.4.9  | CR8X: STN Color Panel Data Format                            |      |

| 6.3.16           | GRA: Offset 178                                 | 6.4.10 | CR9X: TFT Panel Data Format                                  |      |

| 6.3.17           | GRB: Graphics Controller Mode Extensions 79     | 6.4.11 | CRAX: TFT Panel HSYNC Position Contro                        |      |

| 6.3.18           | CR19: Interlace End80                           |        | CRBX: Special Functions                                      |      |

| 6.3.19           | CR1A: Interlace Control81                       |        | 132-Column Alphanumeric Mode                                 |      |

| 6.3.20           | CR1B: Extended Display Controls82               |        | Graphics Hardware Cursor                                     |      |

| 6.3.21           | CR1C: Flat-Panel Interface84                    |        | ELECTRICAL SPECIFICATIONS                                    | 113  |

| 6.3.22           | CR1D: Flat-Panel Display Controls86             |        | Absolute Maximum Ratings                                     |      |

| 6.3.23           | CR1E: Flat-Panel Shading88                      |        | OC Specifications (Digital)                                  |      |

| 6.3.24           |                                                 |        | Output Loading Values                                        |      |

| 6.3.25           | CR20: Power Management91                        |        | DC Specifications (Palette DAC)                              | 116  |

| 6.3.26           |                                                 | 7.5    | DC Specifications (Clock Frequency<br>Synthesizer)           | 116  |

| 6.3.27           | CR23: FPVCC/FPBACK Control and                  |        | DAC Characteristics                                          |      |

|                  | SUSPEND Timer94                                 |        | AC Specifications                                            |      |

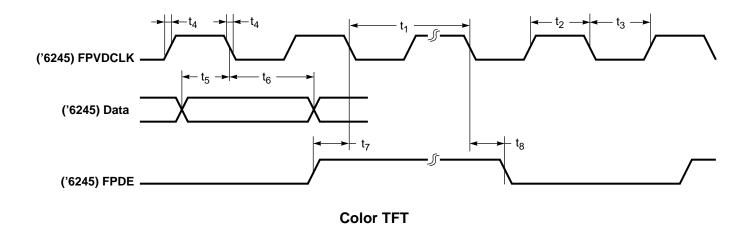

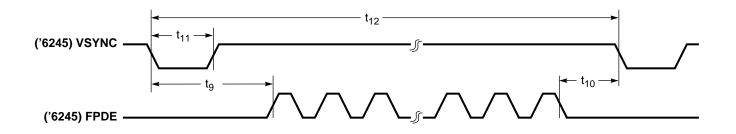

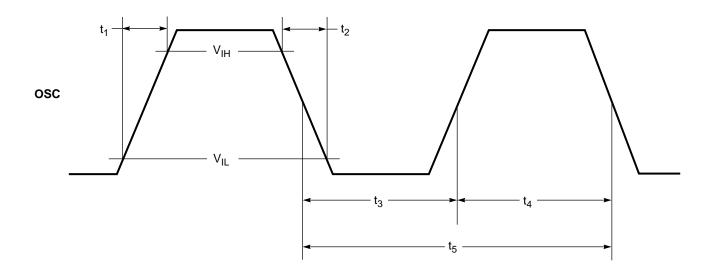

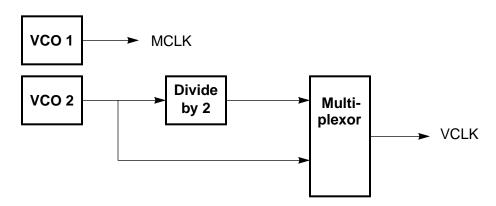

| 6.3.28           |                                                 | 7.7.1  | List of Timing Diagrams                                      |      |

| 6.3.29           | CR27: Chip ID96                                 |        | VCO, MCLK, and VCLK Values                                   |      |

| 6.3.30           | CR29: Part Configuration97                      |        |                                                              |      |

|                  | .CD Timing Registers99                          | 8. I   | PACKAGE SPECIFICATIONS                                       | 141  |

| 6.4.1            | CR0X: Horizontal Total for 80-Column            | 9. (   | ORDERING INFORMATION                                         |      |

| 0.4.0            | Display and Display Mode 13h                    | I      | EXAMPLE                                                      | 142  |

| 6.4.2            | CR1X: Horizontal Total for 40-Column Display100 | Index  | ·                                                            | 143  |

|                  | Display 100                                     | mack   |                                                              | . 70 |

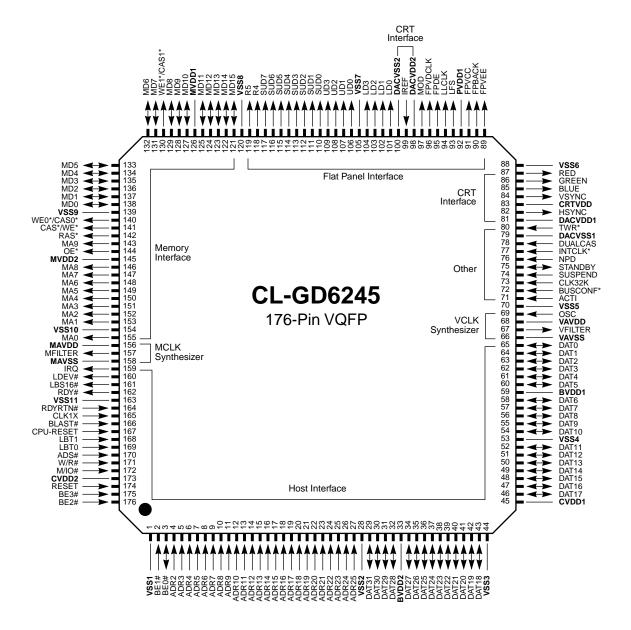

## 1. PIN INFORMATION

The CL-GD6245 VGA controller is available in a 176-pin very-tight-pitch quad flat pack (VQFP) device configuration, shown below.

## 1.1 Pin Diagram

**NOTE:** Power and ground pin names are in bold type.

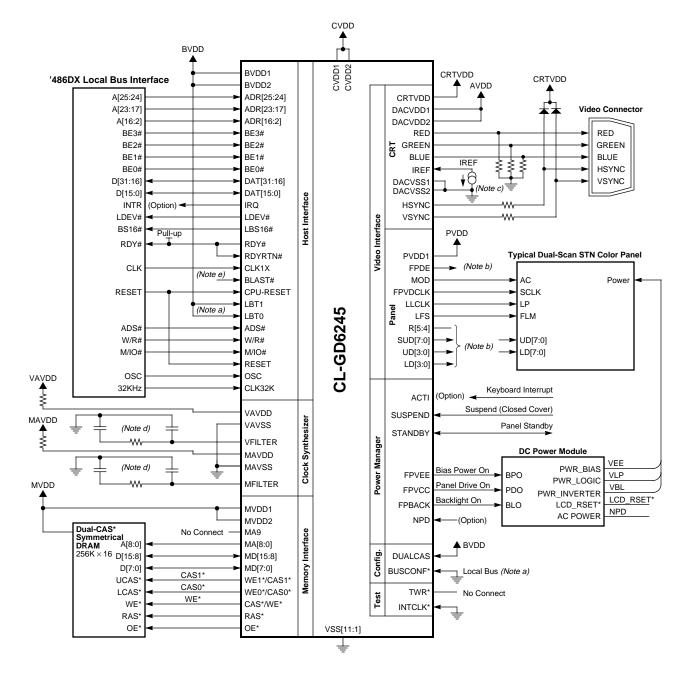

# 1.2 Dual-Scan STN Color Panel Connections — '486DX Local Bus Using 256K $\times$ 16 DRAM with Dual CAS\*

### **NOTES:**

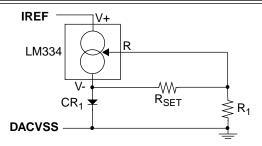

- a. Refer to Table 2-1 for bus configuration.

- b. See the "Panel Interface Connection Table" in the CL-GD6245 Application Book for specific pin connections.

- c. See the application note "IREF Current Source for the CL-GD6245" in the CL-GD6245 Application Book for details on this circuit.

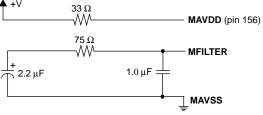

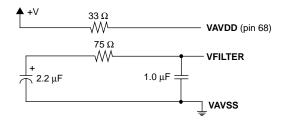

- d. See the application note "CL-GD6245 Analog Voltage Filtering and MFILTER/VFILTER Recommendations" in the *CL-GD6245 Application Book* for details on this circuit.

6 PIN INFORMATION ADVANCE DATA BOOK v1.1 September 1994

e. Ground these input signals when not used.

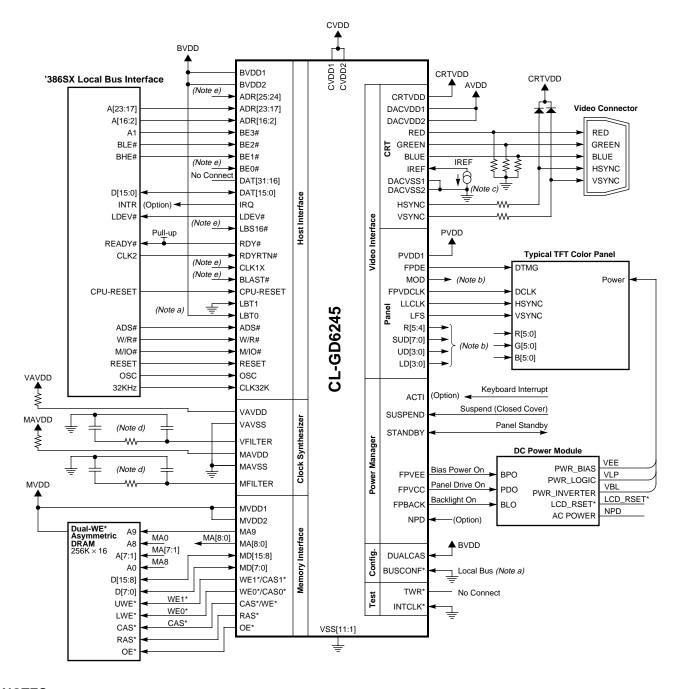

# 1.3 TFT Color Panel Connections — '386SX Local Bus Using 256K $\times$ 16 DRAM with Dual WE\*

## **NOTES:**

- a. Refer to Table 2-1 for bus configuration.

- b. See the "Panel Interface Connection Table" in the CL-GD6245 Application Book for specific pin connections.

- c. See the application note "IREF Current Source for the CL-GD6245" in the CL-GD6245 Application Book for details on this circuit.

- d. See the application note "CL-GD6245 Analog Voltage Filtering and MFILTER/VFILTER Recommendations" in the *CL-GD6245 Application Book* for details on this circuit.

- e. Ground these input signals when not used.

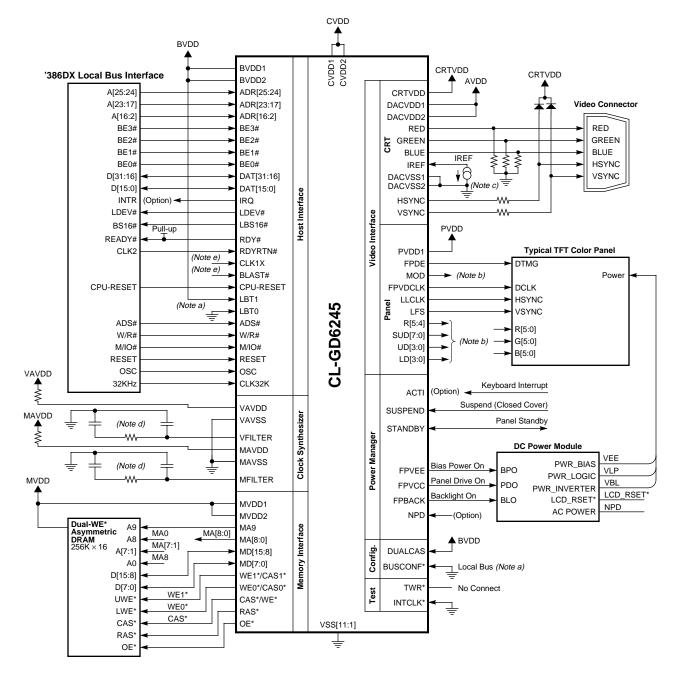

# 1.4 TFT Color Panel Connections — '386DX Local Bus Using 256K $\times$ 16 DRAM with Dual WE\*

#### NOTES:

- a. Refer to Table 2-1 for bus configuration.

- b. See the "Panel Interface Connection Table" in the CL-GD6245 Application Book for specific pin connections.

8 PIN INFORMATION ADVANCE DATA BOOK v1.1 September 1994

- c. See the application note "IREF Current Source for the CL-GD6245" in the CL-GD6245 Application Book for details on this circuit.

- d. See the application note "CL-GD6245 Analog Voltage Filtering and MFILTER/VFILTER Recommendations" in the *CL-GD6245 Application Book* for details on this circuit.

- e. Ground these input signals when not used.

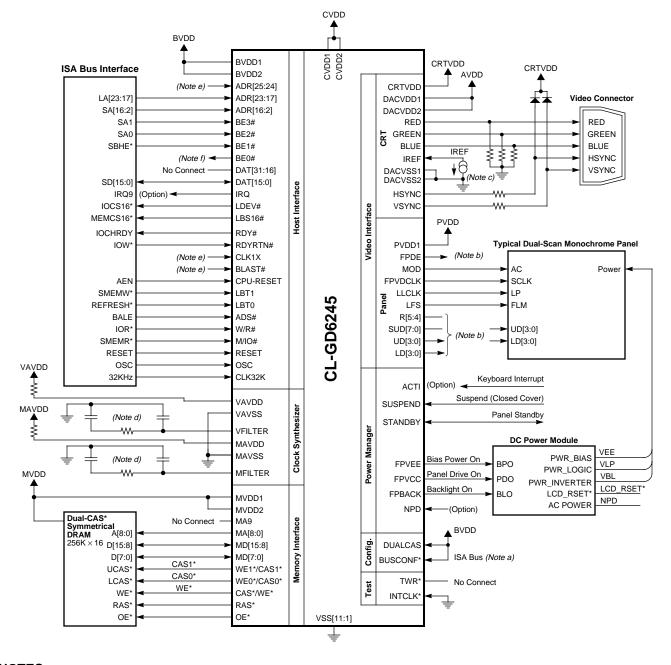

# 1.5 Typical Dual-Scan Monochrome Panel Connections — ISA Bus Using 256K $\times$ 16 DRAM with Dual CAS\*

### NOTES:

a. Refer to Table 2-1 for bus configuration.

ADVANCE DATA BOOK v1.1

- b. See the "Panel Interface Connection Table" in the CL-GD6245 Application Book for specific pin connections.

- c. See the application note "IREF Current Source for the CL-GD6245" in the CL-GD6245 Application Book for details on this cir-

- d. See the application note "CL-GD6245 Analog Voltage Filtering and MFILTER/VFILTER Recommendations" in the CL-GD6245 Application Book for details on this circuit.

- e. Ground these input signals when not used.

- f. BE0# controls the Chip Enable of the optional BIOS EPROMs.

September 1994 PIN INFORMATION ADVANCE DATA BOOK v1.1

## 1.6 Pin Summary

These abbreviations are used for pin types in the following sections:

- (I) indicates input pin.

- (O) indicates output pin.

- (I/O) indicates either an input or output pin, depending on the mode.

- (OC) indicates open-collector output pin.

- (3-S) indicates three-state output pin.

- (#) indicates an active-'low' pin for the host local bus, and (\*) indicates an active-'low' pin for other interfaces.

- (n/c) indicates no connect.

Table 1-1. Host Interface Pins

10

| CL-GD6245 Pin |            | ICA Due             | '386SX                           | '386DX                           | '486          | VESA <sup>®</sup> |              |

|---------------|------------|---------------------|----------------------------------|----------------------------------|---------------|-------------------|--------------|

| Number        | Name       | Туре                | ISA Bus                          | Local Bus                        | Local Bus     | Local Bus         | VL-Bus™      |

| 27:26         | ADR[25:24] | I                   | Tie to ground Tie to ground A[25 |                                  | A[25:24]      | A[25:24]          | ADR[25:24]   |

| 25:19         | ADR[23:17] | I                   | LA[23:17]                        | LA[23:17] A[23:17] A[23:17] A[23 |               | A[23:17]          | ADR[23:17]   |

| 18:4          | ADR[16:2]  | I                   | SA[16:2]                         | A[16:2]                          | A[16:2]       | A[16:2]           | ADR[16:2]    |

| 175           | BE3#       | I                   | SA1                              | A1                               | BE3#          | BE3#              | BE3#         |

| 176           | BE2#       | I                   | SA0                              | BLE#                             | BE2#          | BE2#              | BE2#         |

| 2             | BE1#       | I                   | SBHE*                            | BHE#                             | BE1#          | BE1#              | BE1#         |

| 3             | BE0#       | I (O <sup>a</sup> ) | (Note <sup>a</sup> )             | Tie to ground                    | BE0#          | BE0#              | BE0#         |

| 29–32         | DAT[31:28] | I/O                 | n/c                              | n/c                              | D[31:28]      | D[31:28]          | DAT[31:28]   |

| 34–43         | DAT[27:18] | I/O                 | n/c                              | n/c                              | D[27:18]      | D[27:18]          | DAT[27:18]   |

| 46–47         | DAT[17:16] | I/O                 | n/c                              | n/c                              | D[17:16]      | D[17:16]          | DAT[17:16]   |

| 48–52         | DAT[15:11] | I/O                 | SD[15:11]                        | D[15:11]                         | D[15:11]      | D[15:11]          | DAT[15:11]   |

| 54–58         | DAT[10:6]  | I/O                 | SD[10:6]                         | D[10:6]                          | D[10:6]       | D[10:6]           | DAT[10:6]    |

| 60–65         | DAT[5:0]   | I/O                 | SD[5:0]                          | D[5:0]                           | D[5:0]        | D[5:0]            | DAT[5:0]     |

| 159           | IRQ        | 0                   | IRQ9 or n/c                      | INTR or n/c                      | INTR or n/c   | INTR or n/c       | IRQ9 or n/c  |

| 160           | LDEV#      | OC                  | IOCS16*                          | LDEV#                            | LDEV#         | LDEV#             | LDEV#        |

| 161           | LBS16#     | OC                  | MEMCS16*                         | Tie to ground                    | BS16#         | BS16#             | LBS16#       |

| 162           | RDY#       | 3-S                 | IOCHRDY                          | READY#                           | READY#        | RDY#              | LRDY#        |

| 164           | RDYRTN#    | I                   | IOW#                             | CLK2                             | CLK2          | RDY#              | RDYRTN#      |

| 165           | CLK1X      | I                   | Tie to ground                    | Tie to ground                    | Tie to ground | CLK               | LCLK         |

| 166           | BLAST#     | I                   | Tie to ground                    | Tie to ground                    | Tie to ground | Tie to ground     | BLAST#       |

| 167           | CPU-RESET  | I                   | AEN                              | CPU-RESET                        | CPU-RESET     | RESET             | RESET        |

| 168           | LBT1       | I                   | SMEMW*                           | Tie to ground                    | Tie to BVDD1  | Tie to BVDD1      | Tie to BVDD1 |

| 169           | LBT0       | I                   | REFRESH*                         | Tie to BVDD1                     | Tie to ground | Tie to BVDD1      | Tie to BVDD1 |

| 170           | ADS#       | I                   | BALE                             | ADS#                             | ADS#          | ADS#              | ADS#         |

| 171           | W/R#       | I                   | IOR*                             | W/R#                             | W/R#          | W/R#              | W/R#         |

| 172           | M/IO#      | I                   | SMEMR*                           | M/IO#                            | M/IO#         | M/IO#             | M/IO#        |

| 174           | RESET      | I                   | RESET                            | RESET                            | RESET         | RESET             | RESET        |

<sup>&</sup>lt;sup>a</sup> If an EPROM is used to load the BIOS, the BE0# pin is an active-low output used to control the EPROM Chip Enable.

PIN INFORMATION ADVANCE DATA BOOK v1.1 September 1994

Table 1-2. CRT Interface Pins

|        | CL-GD6245 Pin     | 1          | Description                                        |  |  |

|--------|-------------------|------------|----------------------------------------------------|--|--|

| Number | Name              | Туре       | Description                                        |  |  |

| 82     | HSYNC             | 3-S        | Horizontal synchronization pulse for monitor       |  |  |

| 84     | VSYNC             | 3-S        | Vertical synchronization pulse for monitor         |  |  |

| 85     | BLUE              | Analog Out | Analog current representing Blue value of pixel    |  |  |

| 86     | GREEN             | Analog Out | Analog current representing Green value of pixel   |  |  |

| 87     | RED               | Analog Out | Analog current representing Red value of pixel     |  |  |

| 99     | 99 IREF Analog In |            | DAC current reference — sets full-scale DAC output |  |  |

Table 1-3. LCD Flat-Panel Interface Pins

| CL-GD6245 Pin |         | Monochrome | STN Color              | TFT Color              |                        |  |

|---------------|---------|------------|------------------------|------------------------|------------------------|--|

| Number        | Name    | Туре       | Panel Pin <sup>a</sup> | Panel Pin <sup>a</sup> | Panel Pin <sup>a</sup> |  |

| 119           | R5      | 0          | n/c                    | n/c                    | R5                     |  |

| 118           | R4      | 0          | n/c n/c                |                        | R4                     |  |

| 117           | SUD7    | 0          | n/c                    | SUD7                   | R3                     |  |

| 116           | SUD6    | 0          | n/c                    | SUD6                   | R2                     |  |

| 115           | SUD5    | 0          | n/c                    | SUD5                   | G5                     |  |

| 114           | SUD4    | 0          | n/c                    | SUD4                   | G4                     |  |

| 113           | SUD3    | 0          | n/c                    | SUD3                   | G3                     |  |

| 112           | SUD2    | 0          | n/c                    | SUD2                   | B5                     |  |

| 111           | SUD1    | 0          | n/c                    | SUD1                   | B4                     |  |

| 110           | SUD0    | 0          | n/c                    | SUD0                   | B3                     |  |

| 109           | UD3     | 0          | UD3                    | SLD7                   | R1                     |  |

| 108           | UD2     | 0          | UD2                    | SLD6                   | R0                     |  |

| 107           | UD1     | 0          | UD1                    | SLD5                   | G2                     |  |

| 106           | UD0     | 0          | UD0                    | SLD4                   | G1                     |  |

| 104           | LD3     | 0          | LD3                    | SLD3                   | G0                     |  |

| 103           | LD2     | 0          | LD2                    | SLD2                   | B2                     |  |

| 102           | LD1     | 0          | LD1                    | SLD1                   | B1                     |  |

| 101           | LD0     | 0          | LD0                    | SLD0                   | B0                     |  |

| 97            | MOD     | 0          | MOD                    | MOD                    | MOD                    |  |

| 96            | FPVDCLK | 0          | FPVDCLK                | FPVDCLK                | FPVDCLK                |  |

| 95            | FPDE    | 0          | FPDE                   | n/c                    | FPDE                   |  |

| 94            | LLCLK   | 3-S        | LLCLK                  | LLCLK                  | HSYNC                  |  |

| 93            | LFS     | 3-S        | LFS                    | LFS                    | VSYNC                  |  |

<sup>&</sup>lt;sup>a</sup> For exact pin connections, refer to the panel interface connection tables located in the "Panel Interface Guide" section of the *CL-GD6245 Application Book*.

September 1994 ADVANCE DATA BOOK v1.1 PIN INFORMATION

Table 1-4. Display Memory Interface Pins

|        | CL-GD6245 Pin |      | Dual-WE*                | Dual-CAS*                   |  |

|--------|---------------|------|-------------------------|-----------------------------|--|

| Number | Name          | Туре | DRAM (DUALCAS is 'low') | DRAM<br>(DUALCAS is 'high') |  |

| 143    | MA9           | 0    | MA9 <sup>a</sup>        | MA9 <sup>a</sup>            |  |

| 146    | MA8           | 0    | MA8                     | MA8                         |  |

| 147    | MA7           | 0    | MA7                     | MA7                         |  |

| 148    | MA6           | 0    | MA6                     | MA6                         |  |

| 149    | MA5           | 0    | MA5                     | MA5                         |  |

| 150    | MA4           | 0    | MA4                     | MA4                         |  |

| 151    | MA3           | 0    | MA3                     | MA3                         |  |

| 152    | MA2           | 0    | MA2                     | MA2                         |  |

| 153    | MA1           | 0    | MA1                     | MA1                         |  |

| 155    | MA0           | 0    | MA0 <sup>a</sup>        | MA0 <sup>a</sup>            |  |

| 121    | MD15          | I/O  | MD15                    | MD15                        |  |

| 122    | MD14          | I/O  | MD14                    | MD14                        |  |

| 123    | MD13          | I/O  | MD13                    | MD13                        |  |

| 124    | MD12          | I/O  | MD12                    | MD12                        |  |

| 125    | MD11          | I/O  | MD11                    | MD11                        |  |

| 127    | MD10          | I/O  | MD10                    | MD10                        |  |

| 128    | MD9           | I/O  | MD9                     | MD9                         |  |

| 129    | MD8           | I/O  | MD8                     | MD8                         |  |

| 131    | MD7           | I/O  | MD7                     | MD7                         |  |

| 132    | MD6           | I/O  | MD6                     | MD6                         |  |

| 133    | MD5           | I/O  | MD5                     | MD5                         |  |

| 134    | MD4           | I/O  | MD4                     | MD4                         |  |

| 135    | MD3           | I/O  | MD3                     | MD3                         |  |

| 136    | MD2           | I/O  | MD2                     | MD2                         |  |

| 137    | MD1           | I/O  | MD1                     | MD1                         |  |

| 138    | MD0           | I/O  | MD0                     | MD0                         |  |

| 130    | WE1*/CAS1*    | 0    | WE1*                    | CAS1*                       |  |

| 140    | WE0*/CAS0*    | 0    | WE0*                    | CAS0*                       |  |

| 141    | CAS*/WE*      | 0    | CAS*                    | WE*                         |  |

| 142    | RAS*          | 0    | RAS*                    | RAS*                        |  |

| 144    | OE*           | 0    | OE*                     | OE*                         |  |

<sup>&</sup>lt;sup>a</sup> MA9 and MA0 are not used to drive column addresses on asymmetrical DRAMs. For a detailed explanation, see the application note "A Single-DRAM LCD Motherboard Solution for Monochrome/Color Notebook Computers" in the *CL-GD6245 Application Book*.

Table 1-5. Miscellaneous Pins

| CL-GD6245 Pin |          |      | Description                                        |  |

|---------------|----------|------|----------------------------------------------------|--|

| Number        | Name     | Туре | - Description                                      |  |

| 72            | BUSCONF* | Į    | Bus configuration select (used with LBT0 and LBT1) |  |

| 77            | INTCLK*  | I    | Internal clock enable                              |  |

| 78            | DUALCAS  | I    | Dual-CAS* or dual-WE* DRAM select                  |  |

| 80 TWR* I     |          | I    | Test write enable (used for testing only)          |  |

**Table 1-6.** Power Management Pins

|        | CL-GD6245 Pin |      | Description                                       |  |  |  |

|--------|---------------|------|---------------------------------------------------|--|--|--|

| Number | Name          | Туре | Description                                       |  |  |  |

| 91     | FPVCC         | 0    | Panel power-on enable                             |  |  |  |

| 90     | FPBACK        | 0    | Backlight power-on enable                         |  |  |  |

| 89     | FPVEE         | 0    | Bias power-on enable                              |  |  |  |

| 76     | NPD           | I    | No power-down (disable power-down timers)         |  |  |  |

| 75     | STANDBY       | I/O  | Standby mode control/standby status               |  |  |  |

| 74     | SUSPEND       | I    | Suspend mode control (close-cover power sequence) |  |  |  |

| 71     | ACTI          | I    | Activity indicator (reset power-down timers)      |  |  |  |

Table 1-7. Dual-Frequency Synthesizer Interface Pins

| CL-GD6245 Pin         |         |            | Description                                                           |  |  |

|-----------------------|---------|------------|-----------------------------------------------------------------------|--|--|

| Number                | Name    | Туре       | Description                                                           |  |  |

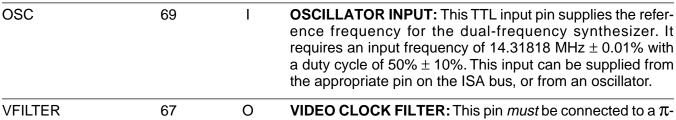

| 69                    | OSC     | I          | Oscillator input for dual-frequency synthesizer                       |  |  |

| 73                    | CLK32K  | I          | Optional 32-kHz clock input for video RAM refresh during Suspend mode |  |  |

| 157                   | MFILTER | Analog Out | Memory clock filter connection                                        |  |  |

| 67 VFILTER Analog Out |         | Analog Out | Video clock filter connection                                         |  |  |

September 1994 ADVANCE DATA BOOK v1.1 PIN INFORMATION

Table 1-8. Power and Ground Pins

| CL-GD                    | CL-GD6245 Pin |                          | Bypass            | Video Controller Section                                                                            |  |  |

|--------------------------|---------------|--------------------------|-------------------|-----------------------------------------------------------------------------------------------------|--|--|

| Number                   | Name          | to Rail                  | Capacitor         | Serviced by Power Pins                                                                              |  |  |

| 59                       | BVDD1         | VDD(VCC)                 | 0.1 μF            | Digital valte on factors interfered and start                                                       |  |  |

| 33                       | BVDD2         | VDD(VCC)                 | 0.1 μF            | Digital voltage for bus interface section                                                           |  |  |

| 45                       | CVDD1         | VDD(VCC)                 | 0.1 μF            | Digital valtage for care legic of controller                                                        |  |  |

| 173                      | CVDD2         | VDD(VCC)                 | 0.1 μF            | Digital voltage for core logic of controller                                                        |  |  |

| 83                       | CRTVDD        | VDD(VCC)                 | 10 μF             | Digital voltage for CRT output pins                                                                 |  |  |

| 81                       | DACVDD1       | VDD(VCC)                 | 10 μF             | Analog voltage for polette DAC                                                                      |  |  |

| 98                       | DACVDD2       | VDD(VCC)                 | 10 μF             | Analog voltage for palette DAC                                                                      |  |  |

| 156                      | MAVDD         | VDD(VCC)<br>through 33 Ω | 10 μF to<br>MAVSS | Analog voltage for memory clock synthesizer                                                         |  |  |

| 126                      | MVDD1         | VDD(VCC)                 | 0.1 μF            | Digital valtage for mamory interface costion                                                        |  |  |

| 145                      | MVDD2         | VDD(VCC)                 | 0.1 μF            | Digital voltage for memory interface section                                                        |  |  |

| 92                       | PVDD1         | VDD(VCC)                 | 0.1 μF            | Digital voltage for LCD panel interface section                                                     |  |  |

| 68                       | VAVDD         | VDD(VCC)<br>through 33 Ω | 10 μF to<br>VAVSS | Analog voltage for video clock synthesizer                                                          |  |  |

| 79                       | DACVSS1       | Analog ground            |                   |                                                                                                     |  |  |

| 100                      | DACVSS2       | Analog ground            |                   | The analog ground plane should be isolated from the VSS (digital) ground plane to prevent noise and |  |  |

| 158                      | MAVSS         | Analog ground            |                   | crosstalk.                                                                                          |  |  |

| 66                       | VAVSS         | Analog ground            |                   |                                                                                                     |  |  |

| 1                        | VSS1          | Digital ground           |                   |                                                                                                     |  |  |

| 28                       | VSS2          | Digital ground           |                   |                                                                                                     |  |  |

| 44                       | VSS3          | Digital ground           |                   |                                                                                                     |  |  |

| 53                       | VSS4          | Digital ground           |                   |                                                                                                     |  |  |

| 70                       | VSS5          | Digital ground           |                   |                                                                                                     |  |  |

| 88                       | VSS6          | Digital ground           |                   |                                                                                                     |  |  |

| 105                      | VSS7          | Digital ground           |                   |                                                                                                     |  |  |

| 120                      | VSS8          | Digital ground           |                   |                                                                                                     |  |  |

| 139                      | VSS9          | Digital ground           |                   |                                                                                                     |  |  |

| 154 VSS10 Digital ground |               |                          |                   |                                                                                                     |  |  |

| 163                      | VSS11         | Digital ground           |                   |                                                                                                     |  |  |

14 PIN INFORMATION ADVANCE DATA BOOK v1.1 September 1994

## 2. DETAILED PIN DESCRIPTIONS

These abbreviations are used for pin types in the following sections:

- (I) indicates input pin.

- (O) indicates output pin.

- (I/O) indicates either an input or output pin, depending on the mode.

- (OC) indicates open-collector output pin.

- (3-S) indicates three-state output pin.

- (#) indicates an active-low pin for the host local bus, and (\*) indicates an active-low pin for other interfaces.

- Programmable levels '1' and '0' are equivalent to logic levels high and low, respectively.

#### 2.1 Host Interface Pins

The CL-GD6245 can interface directly with the ISA bus, the local buses for the '386SX, '386DX, and '486SX/DX, and the VESA VL-Bus. The bus type is selected with the BUSCONF\*, LBT0, and LBT1 pins, as shown in Table 2-1.

Table 2-1. Host-Bus Configurations

| Bus Type BUSCONF* (Pin 72) |               | LBT0<br>(Pin 169)          | LBT1<br>(Pin 168)        |  |

|----------------------------|---------------|----------------------------|--------------------------|--|

| ISA bus                    | Tie to BVDD1  | Tie to ISA bus<br>REFRESH* | Tie to ISA bus<br>SMEMW* |  |

| '386SX                     | Tie to ground | Tie to BVDD1               | Tie to ground            |  |

| '386DX                     | Tie to ground | Tie to ground              | Tie to BVDD1             |  |

| '486SX/DX                  | Tie to ground | Tie to BVDD1               | Tie to BVDD1             |  |

| VL-Bus™                    | Tie to ground | Tie to BVDD1               | Tie to BVDD1             |  |

Pin descriptions for the host bus interface is divided into two sections, depending on the setting of the BUSCONF\* pin, for either local or ISA bus.

September 1994 ADVANCE DATA BOOK v1.1 DETAILED PIN DESCRIPTIONS

## 2.1.1 ISA-Bus-Mode Host Interface Pins

| Pin Name   | ISA Signal<br>Name | Pin No. | Туре | Description                                                                                                                                                                                                                                                                                                                                                                          |              |                                  |                                             |  |

|------------|--------------------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------|---------------------------------------------|--|

| BUSCONF*   | -                  | 72      | I    | <b>BUS CONFIGURATION*:</b> This active-low pin is used wit the LBT0 and LBT1 pins to choose the CL-GD6245 host bus type. ISA bus configuration is set according to the following table.                                                                                                                                                                                              |              |                                  |                                             |  |

|            |                    |         |      | Table 2-2. ISA Host-Bus Configuration                                                                                                                                                                                                                                                                                                                                                |              |                                  |                                             |  |

|            |                    |         |      | Bus Type   BUSCONF*                                                                                                                                                                                                                                                                                                                                                                  |              |                                  |                                             |  |

|            |                    |         |      | ISA bus                                                                                                                                                                                                                                                                                                                                                                              | Tie to BVDD1 | Tie to ISA bus<br>REFRESH*       | Tie to ISA bus<br>SMEMW*                    |  |

| ADR[23:17] | LA[23:17]          | 25:19   | I    | ADDRESS [23:17]: These inputs extend the system address to 24 bits. They are used, along with ADR[16:2], BE3#, and BE2#, to select the resource to be accessed during memory and I/O operations. Data on the ADR[23:17] pins is loaded into the internal address latch while ADS# (BALE) is high, and is stored in the latch during the logic high-to-low transition of ADS# (BALE). |              |                                  |                                             |  |

| ADR[16:2]  | SA[16:2]           | 18:4    | I    | ADR[23:17],                                                                                                                                                                                                                                                                                                                                                                          | BE3#, and BE |                                  | sed, along with<br>e resource to be<br>ons. |  |

|            |                    |         |      |                                                                                                                                                                                                                                                                                                                                                                                      |              | ot latched by the stable through | ne CL-GD6245,<br>out the cycle.             |  |

| BE3#, BE2# | SA[1:0]            | 176:175 | I    | <b>BYTE ENABLE [3:2]#:</b> When ISA bus is selected, these bits are used as address inputs, along with ADR[23:17 and ADR[16:2], to select the resource to be accessed during memory and I/O operations.                                                                                                                                                                              |              |                                  |                                             |  |

|            |                    |         |      |                                                                                                                                                                                                                                                                                                                                                                                      |              | ot latched by the stable through | ne CL-GD6245,<br>out the cycle.             |  |

DETAILED PIN DESCRIPTIONS

ADVANCE DATA BOOK v1.1

September 1994

# 2.1.1 ISA-Bus-Mode Host Interface Pins (cont.)

| Pin Name  | ISA Signal<br>Name | Pin No.         | Туре | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                       | n                                      |                                                                                                                                    |                                                 |  |  |

|-----------|--------------------|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|--|

| BE1#      | SBHE*              | 2               | I    | BYTE ENABLE 1#: This active-low input is used, along with BE2#, to determine the width and alignment of a data transfer. BE1# and BE2# are decoded as shown in Table 2-3. In an 8-bit environment, tie BE1# high.                                                                                                                                                                                                                |                                        |                                                                                                                                    |                                                 |  |  |

|           |                    |                 |      | Table 2-3. BE1#/BE2# Decoding                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |                                                                                                                                    |                                                 |  |  |

|           |                    |                 |      | BE1#                                                                                                                                                                                                                                                                                                                                                                                                                             | BE2#                                   | Function                                                                                                                           |                                                 |  |  |

|           |                    |                 |      | low                                                                                                                                                                                                                                                                                                                                                                                                                              | low                                    | 16-bit transfer                                                                                                                    |                                                 |  |  |

|           |                    |                 |      | low                                                                                                                                                                                                                                                                                                                                                                                                                              | high                                   | Upper-byte transfer                                                                                                                |                                                 |  |  |

|           |                    |                 |      | high                                                                                                                                                                                                                                                                                                                                                                                                                             | low                                    | Lower-byte transfer                                                                                                                |                                                 |  |  |

| BEO#      | EROM*              | 3               | 0    | BYTE ENABLE 0#: When the ISA bus is selected, BE0# is an active-low <i>output</i> gated with LBT1 to control the Output Enable pins of up to two 8-bit bus drivers. These drivers are used to connect the data pins of the optional BIOS EPROMs to the system data bus. This output goes active only for memory-read cycles to the address range C000:0–C7FF:F.  The BE0# output is forced to high-impedence when RESET is high. |                                        |                                                                                                                                    |                                                 |  |  |

| DAT[15:8] | SD[15:8]           | 48–52,<br>54–56 | I/O  | data during<br>can be con<br>pins. The D                                                                                                                                                                                                                                                                                                                                                                                         | 16-bit me<br>nected dir<br>AT[15:8] pi | idirectional pins are us<br>mory or I/O operations<br>ectly to the correspon<br>ns have internal pull-u<br>It level when not conne | s. These pins<br>ding ISA bus<br>p resistors to |  |  |

| DAT[7:0]  | SD[7:0]            | 57–58<br>60–65  | I/O  | data during                                                                                                                                                                                                                                                                                                                                                                                                                      | memory o                               | directional pins are user I/O operations. These he corresponding ISA                                                               | e pins can be                                   |  |  |

| CPU-RESET | AEN                | 167             | I    | current cyc<br>will not res                                                                                                                                                                                                                                                                                                                                                                                                      | e is a DMA<br>pond to I/0              | nis input is high, it indic<br>a cycle. In this case, the<br>O cycles. There is no<br>ich still performs refres                    | e CL-GD6245<br>effect on the                    |  |  |

| ADS#      | BALE               | 170             | I    | is loaded in high. Durin                                                                                                                                                                                                                                                                                                                                                                                                         | nto the into<br>g the logic            | ROBE: Data on the AD ernal address latch w high-to-low transition 7] pins is stored in the a                                       | hile ADS# is of ADS#, the                       |  |  |

September 1994 ADVANCE DATA BOOK v1.1 DETAILED PIN DESCRIPTIONS

# 2.1.1 ISA-Bus-Mode Host Interface Pins (cont.)

| Pin Name                                                                                                                                                                                                                                                                                                                                                                                                                         | ISA Signal<br>Name | Pin No.                                                                                                                                                                                                                                 | Туре | Description                                                                                                                                                                                                                                                                                                                                                        |                          |                                                                                        |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------|--|

| RDY#                                                                                                                                                                                                                                                                                                                                                                                                                             | IOCHRDY            | 162                                                                                                                                                                                                                                     | 3-S  | READY#: This output cycles.                                                                                                                                                                                                                                                                                                                                        | t is high during I/O and | d BIOS read                                                                            |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    | During a display-memory read cycle, this output driven low as soon as M/IO# (SMEMR*) goes the data bits are ready to be placed on the Sybus, this output goes high. It remains high ut (SMEMR*) goes high. It then goes high-impedation |      |                                                                                                                                                                                                                                                                                                                                                                    |                          |                                                                                        |  |

| During a display-memory write cycle, if there the Write Buffer, this output is driven high (SMEMW*) goes low. If the Write Buffer is ful (SMEMW*) goes low, LDEV# is driven low low until there is space in the buffer. This outp indicates that additional wait states must be the current display-memory read or write there is space in the Write Buffer, RDY# go remains high, until LBT1 (SMEMW*) goes goes high-impedance. |                    |                                                                                                                                                                                                                                         |      |                                                                                                                                                                                                                                                                                                                                                                    |                          | when LBT1 I when LBT1 and remains ut, when low, inserted into cycle. Once es high, and |  |

| LDEV#                                                                                                                                                                                                                                                                                                                                                                                                                            | IOCS16*            | 160                                                                                                                                                                                                                                     | OC   | LOCAL BUS DEVICE#: This open-collector output driven low to indicate the CL-GD6245 can execute a 16-I/O operation at the address currently on the bus. This oput is generated from a decode of ADR[16:2], BE3 BE2#, and CPU-RESET (AEN). Table 2-4 shows that range of I/O addresses for which LDEV# will go low. In 8-bit environment, this pin is not connected. |                          |                                                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |                                                                                                                                                                                                                                         |      | Table 2-4. LDEV# I/                                                                                                                                                                                                                                                                                                                                                | O Addresses              |                                                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |                                                                                                                                                                                                                                         |      | I/O Addresses                                                                                                                                                                                                                                                                                                                                                      | Function                 |                                                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |                                                                                                                                                                                                                                         |      | 3C4, 3C5                                                                                                                                                                                                                                                                                                                                                           | Sequencer                |                                                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |                                                                                                                                                                                                                                         |      | 3CE, 3CF                                                                                                                                                                                                                                                                                                                                                           | Graphics controller      |                                                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |                                                                                                                                                                                                                                         |      | 3B4/3D4, 3B5/3D5                                                                                                                                                                                                                                                                                                                                                   | CRT controller           |                                                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |                                                                                                                                                                                                                                         |      | 3BA/3DA                                                                                                                                                                                                                                                                                                                                                            | Input Status register 1  |                                                                                        |  |

| W/R#                                                                                                                                                                                                                                                                                                                                                                                                                             | IOR*               | 171                                                                                                                                                                                                                                     | I    | WRITE/READ#: This active-low input is forced low by the host to request an I/O data transfer. When the address or ADR[16:2], BE3#, and BE2# is within the range of the CL-GD6245, the CL-GD6245 responds by placing the contents of the appropriate register on the System Data bus.                                                                               |                          |                                                                                        |  |

September 1994 ADVANCE DATA BOOK v1.1

18

# 2.1.1 ISA-Bus-Mode Host Interface Pins (cont.)

| Pin Name | ISA Signal<br>Name | Pin No. | Туре | Description                                                                                                                                                                                                                                                                                                                              |

|----------|--------------------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDYRTN#  | IOW*               | 164     | I    | <b>READY RETURN#:</b> This active-low input is forced low by the host to initiate an I/O data write to the CL-GD6245. When the address on ADR[16:2], BE3#, and BE2# is within the range of the CL-GD6245, the contents of the System Data bus is written into the addressed register during the logic low-to-high transition of RDYRTN#. |

|          |                    |         |      | A list of I/O addresses that the CL-GD6245 responds to appears in Table 2-4. When a 16-bit I/O write is performed, the specified address is typically the Index register for one of the VGA groups. In this case, the index should appear on DAT[7:0], and the data should appear on DAT[15:8].                                          |

| IRQ      | IRQ9               | 159     | 3-S  | <b>INTERRUPT REQUEST:</b> This output is typically unused in an ISA-bus design, but it can be connected to IRQ9 if needed. Register CR11 controls the interrupt function.                                                                                                                                                                |

| LBS16#   | MEMCS16*           | 161     | OC   | LOCAL BUS SIZE 16#: This open-collector output is driven low to indicate that the CL-GD6245 can execute a 16-bit memory operation at the address currently on the bus. Table 2-5 summarizes the conditions for which LBS16# goes low. In an 8-bit environment, this pin is not connected.                                                |

Table 2-5. LBS16# Addresses

| Resource                | Address<br>Bits | Address<br>Range | Qualifier                               |

|-------------------------|-----------------|------------------|-----------------------------------------|

| Display<br>Mode 3       | ADR[23:17]      | B800:0-BFFF:F    | SR8[6] = high<br>(no other VGA<br>card) |

| Display<br>Mode 7       | ADR[23:17]      | B000:0-B7FF:F    | SR8[6] = high<br>(no other VGA<br>card) |

| All other display modes | ADR[23:17]      | A000:0-BFFF:F    | SR8[6] = high<br>(no other VGA<br>card) |

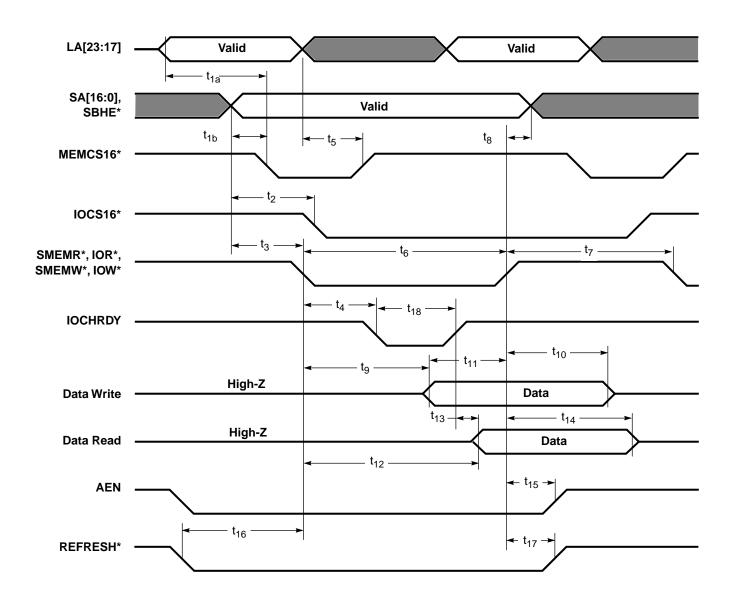

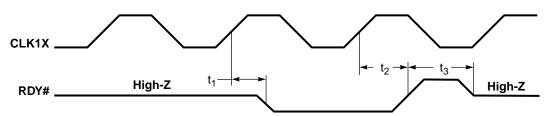

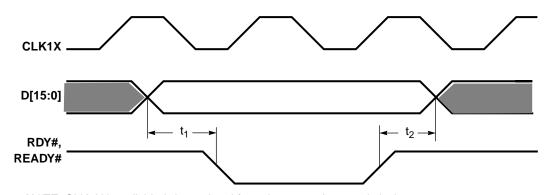

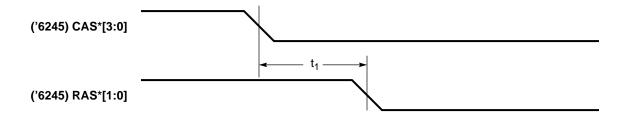

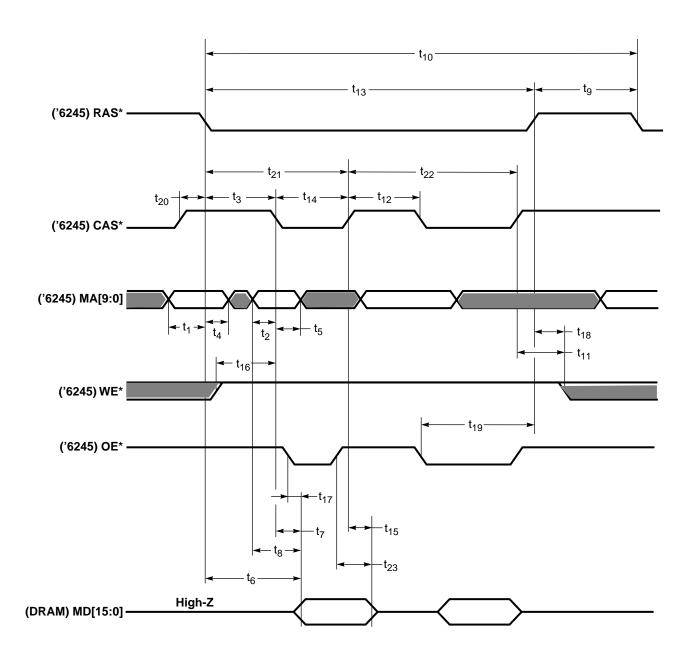

| LBT0 | REFRESH* | 169 I | LOCAL BUS TYPE 0: When used with the ISA bus, this            |