# DP8228/DP8228M/DP8238/DP8238M System Controller and Bus Driver

### **General Description**

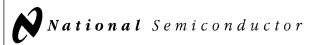

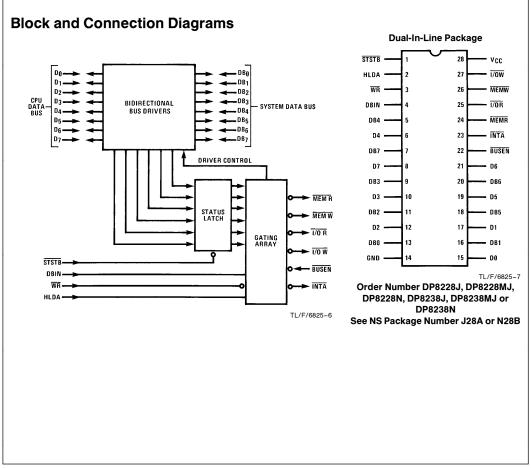

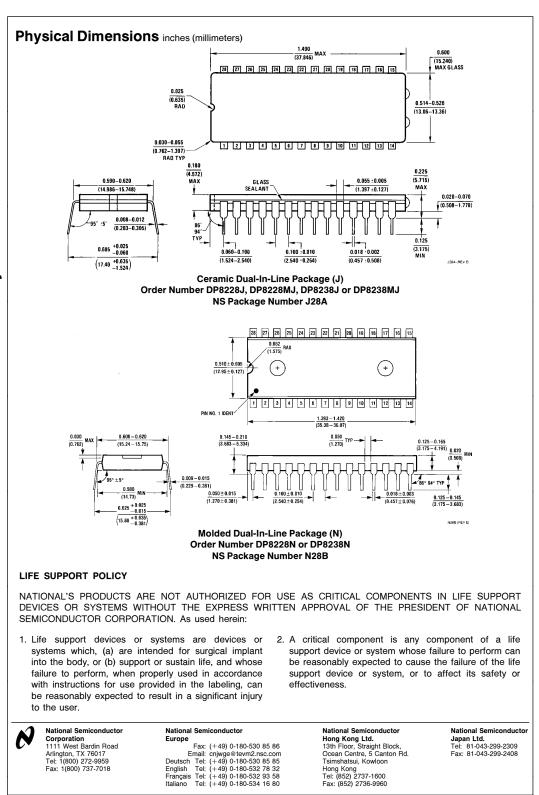

The DP8228/DP8228M, DP8238/DP8238M are system controller/bus drivers contained in a standard, 28-pin dualin-line package. The chip, which is fabricated using Schottky Bipolar technology, generates all the read and write control signals required to directly interface the memory and input/ output components of the 8080A microcomputer family. The chip also provides drive and isolation for the bidirectional data bus of the 8080A microprocessor. Data bus isolation enables the use of slower memory and input/output components in a system, and provides for enhanced system noise immunity.

A user-selected signal-level interrupt vector (RST 7) is provided by the device for use in the interrupt structure of small systems that need only one basic vector. No additional components (such as an interrupt instruction port) are required to use the single interrupt vector in these systems. The devices also generate an Interrupt Acknowledge (INTA) control signal for each byte of a multibyte CALL instruction

when an interrupt is acknowledged by the 8080A. This feature permits the use of a multilevel priority interrupt structure in large, interrupt-driven systems.

#### Features

- Single chip system controller and bus driver for 8080A Microcomputer Systems

- Allows use of multibyte CALL instructions for Interrupt Acknowledge

- Provides user-selected single-level interrupt vector (RST 7)

- Provides isolation of data bus

- Supports a wide variety of system bus structures

- Reduces system component count

- DP8238/DP8238M provides advanced Input/Output Write and Memory Write control signals for large system timing control

© 1995 National Semiconductor Corporation TL/F/6825

RRD-B30M105/Printed in U. S. A.

December 1988

DP8228/DP8228M/DP8238/DP8238M System Controller and Bus Driver

## Absolute Maximum Ratings

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Storage Temperature                                                     | -65°C to +150°C         |

|-------------------------------------------------------------------------|-------------------------|

| Supply Voltage, V <sub>CC</sub>                                         | -0.5 to $+7V$           |

| Input Voltage                                                           | -1.5V to $+7V$          |

| Output Current                                                          | 100 mA                  |

| Maximum Power Dissipation* at 25°C                                      |                         |

| Cavity Package                                                          | 2179 mW                 |

| Molded Package                                                          | 2361 mW                 |

| *Derate cavity package 14.5 mW/°C above 25°C;<br>18.9 mW/°C above 25°C. | ; derate molded package |

## **Operating Conditions**

|                                         | Min             | Max  | Units           |

|-----------------------------------------|-----------------|------|-----------------|

| Supply Voltage (V <sub>CC</sub> )       |                 |      |                 |

| DP8228M, DP8238M                        | 4.50            | 5.50 | V <sub>DC</sub> |

| DP8228, DP8238                          | 4.75            | 5.25 | V <sub>DC</sub> |

| Operating Temperature (T <sub>A</sub> ) |                 |      |                 |

| DP8228M, DP8238M                        | -55             | +125 | °C              |

| DP8228, DP8238                          | 0               | +70  | °C              |

| Nata Mandana anti-                      | 4 - 11 - 14 - 1 |      |                 |

Note: Maximum ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not intended and should be limited to those conditions specified under DC electrical characteristics.

# $\label{eq:constraint} \textbf{Electrical Characteristics} \; \mathsf{Min} \leq \mathsf{T}_A \leq \mathsf{Max}, \mathsf{Min} \leq \mathsf{V}_{CC} \leq \mathsf{Max}, \mathsf{unless otherwise noted} \;$

| Symbol          | Param                               | eter                                               | Conditions                                                             |                              |     | Typ<br>(Note 1) | Мах  | Units |

|-----------------|-------------------------------------|----------------------------------------------------|------------------------------------------------------------------------|------------------------------|-----|-----------------|------|-------|

| V <sub>C</sub>  | Input Clamp Voltage,                | All Inputs                                         | $V_{CC} = Min, I_C = -5 mA$                                            |                              |     | 0.6             | -1.0 | V     |

| ١ <sub>F</sub>  | Input Load                          | STSTB                                              | V <sub>CC</sub> = Max                                                  |                              |     |                 | 500  | μA    |

|                 | Current                             | D2 and D6                                          | $V_F = 0.45V$ for DP8228, DP8238<br>$V_F = 0.40V$ for DP8228M, DP8238M |                              |     |                 | 750  | μΑ    |

|                 |                                     | D0, D1, D4,<br>D5 and D7                           |                                                                        |                              |     |                 | 250  | μΑ    |

|                 |                                     | All Other<br>Inputs                                |                                                                        |                              |     |                 | 250  | μΑ    |

| I <sub>R</sub>  | Input Leakage                       | DB0-DB7                                            | $V_{CC} = Max, V_{R}$                                                  | = V <sub>CC</sub>            |     |                 | 20   | μA    |

| Current         |                                     | All Other<br>Inputs                                |                                                                        |                              |     |                 | 100  | μΑ    |

| $V_{TH}$        | Input Threshold Volta<br>All Inputs | ge,                                                | $V_{CC} = 5V$                                                          |                              | 0.8 |                 | 2.0  | v     |

| Icc             | Power Supply Current                |                                                    | V <sub>CC</sub> = Max                                                  | DP8228, DP8238               |     | 185             | 230  | mA    |

|                 |                                     |                                                    |                                                                        | DP8228M, DP8238M             |     | 160             | 230  | mA    |

| V <sub>OL</sub> | Output Low<br>Voltage               | D0-D7                                              | $V_{CC} = Min,$                                                        | DP8228M, DP8238M             |     |                 | 0.50 | V     |

|                 |                                     |                                                    | $I_{OL} = 2 \text{ mA}$                                                | DP8228, DP8238               |     |                 | 0.45 | V     |

|                 |                                     | All Other                                          | $V_{CC} = Min,$<br>$I_{OL} = 10 \text{ mA}$                            | DP8228M, DP8238M             |     |                 | 0.50 | v     |

|                 |                                     | Outputs                                            |                                                                        | DP8228, DP8238               |     |                 | 0.45 | V     |

| V <sub>OH</sub> | Output High                         | Output High $D0-D7$ $V_C = Min$ , DP8228M, DP8238I |                                                                        | DP8228M, DP8238M             | 3.3 | 3.8             |      | V     |

|                 |                                     |                                                    | $I_{OL} = -10 \ \mu A$                                                 | DP8228, DP8238               | 3.6 | 3.8             |      | V     |

|                 |                                     | All Other<br>Outputs                               | $V_{CC} = Min, I_{OH} = -1 mA$                                         |                              |     | 3.8             |      | v     |

| I <sub>OS</sub> | Short Circuit Current,              | All Outputs                                        | $V_{CC} = 5V, V_O = 0V$                                                |                              | 15  |                 | 90   | mA    |

| IO (OFF)        | OFF State Output Cur                | FF State Output Current V                          |                                                                        | $V_{CC} = Max, V_O = V_{CC}$ |     |                 | 100  | μΑ    |

|                 | All Control Outputs                 |                                                    | $V_{CC} = Max, V_O = 0.45V$                                            |                              |     |                 | -100 | μA    |

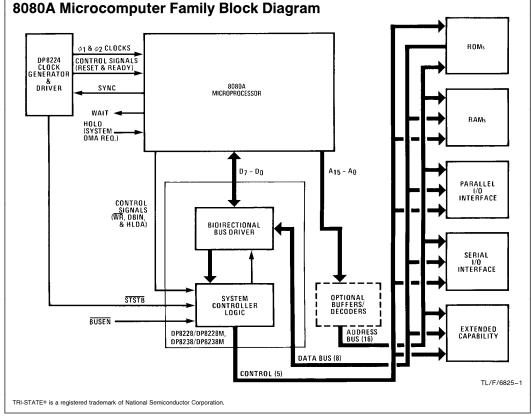

| IINT            | INTA Current                        |                                                    | (See Test Conditions, Figure 3)                                        |                              |     |                 | 5    | mA    |

| Symbol                            | Parameter                                                                                                  | Min                                   |     | Typ<br>(Note 1) |     |              | Units |  |

|-----------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------|-----|-----------------|-----|--------------|-------|--|

| C <sub>IN</sub> Input Capacitance |                                                                                                            |                                       |     | 8               | 12  |              | pF    |  |

| C <sub>OUT</sub>                  | Output Capacitance Control Signals                                                                         |                                       | 7   |                 | 15  |              | pF    |  |

| I/O                               | I/O Capacitance (D or DB)                                                                                  |                                       | 8   |                 | 15  |              | pF    |  |

| ·                                 | er is periodically sampled and not 100% tested.<br>ing Characteristics $Min \le V_{CC} \le 1$<br>Parameter | Max, Min $\leq T_A \leq 1$ Conditions | DP8 | 228M,<br>238M   |     | 228,<br>3238 | Unit  |  |

|                                   |                                                                                                            |                                       | Min | Max             | Min | Max          |       |  |

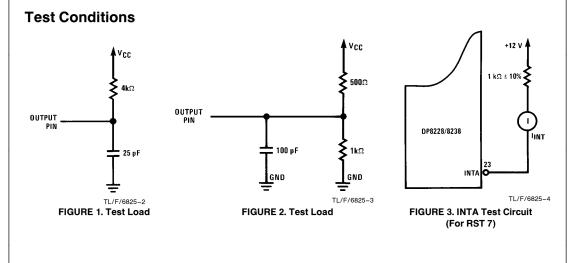

| t <sub>PW</sub>                   | Width of Status Strobe                                                                                     |                                       | 25  |                 | 22  |              | ns    |  |

| t <sub>SS</sub>                   | Set-Up Time, Status Inputs D0-D7                                                                           |                                       | 8   |                 | 8   |              | ns    |  |

| t <sub>SH</sub>                   | Hold Time, Status Inuts D0-D7                                                                              |                                       | 5   |                 | 5   |              | ns    |  |

| t <sub>DC</sub>                   | Delay from STSTB to Any Control Signal                                                                     | (Figure 2)                            | 20  | 75              | 20  | 60           | ns    |  |

| t <sub>RR</sub>                   | Delay from DBIN to Control Outputs                                                                         | (Figure 2)                            |     | 30              |     | 30           | ns    |  |

| t <sub>RE</sub>                   | Delay from DBIN to Enable/<br>Disable 8080 Bus                                                             | (Figure 1)                            |     | 45              |     | 45           | ns    |  |

| t <sub>RD</sub>                   | Delay from System Bus to 8080<br>Bus During Read                                                           | (Figure 1)                            |     | 45              |     | 30           | ns    |  |

| t <sub>WR</sub>                   | Delay from $\overline{WR}$ to Control Outputs                                                              | (Figure 2)                            | 5   | 60              | 5   | 45           | ns    |  |

| twe                               | Delay to Enable System Bus<br>DB0-DB7 after STSTB                                                          | (Figure 2)                            |     | 30              |     | 30           | ns    |  |

| t <sub>WD</sub>                   | Delay from 8080 Bus D0–D7 to<br>System Bus DB0–DB7 During Write                                            | (Figure 2)                            | 5   | 40              | 5   | 40           | ns    |  |

| t <sub>E</sub>                    | Delay from System Bus Enable to<br>System Bus DB0–DB7                                                      | (Figure 2)                            |     | 30              |     | 30           | ns    |  |

| t <sub>HD</sub>                   | HLDA to Read Status Outputs                                                                                | (Figure 2)                            |     | 25              |     | 25           | ns    |  |

| t <sub>DS</sub>                   | Set-Up Time, System Bus Inputs to HLDA                                                                     |                                       | 10  |                 | 10  |              | ns    |  |

|                                   | Hold Time, System Bus Inputs to HLDA                                                                       |                                       | 20  |                 | 20  |              | ns    |  |

**VOLTAGE MEASUREMENT POINTS:**  $D_0-D_7$  (when outputs) Logic "0" = 0.8V, Logic "0" = 0.8V, Logic "1" = 3.0V. All other signals measured at 1.5V. \*Advanced  $\overline{I/OW}$  MEMW for 8238 only.

### **Functional Pin Definitions**

The following describes the function of all of the DP8228/ DP8228M, DP8238/DP8238M pinouts. Some of these descriptions reference internal circuits.

#### INPUT SIGNALS

Status Strobe ( $\overline{STSTB}$ ): Activated (low) at the start of each new machine cycle. The  $\overline{STSTB}$  input is used to store a status word (refer to chart) from the 8080A microprocessor into the internal status latch of the DP8228, DP8238. The status word is latched when the  $\overline{STSTB}$  returns to the high state. The 8080A outputs this status word onto its data bus during the first state (SYNC interval) of each machine cycle.

**Data Bus In (DBIN):** When high, indicates that the 8080A data bus is in the input mode. The DBIN signal is used to gate data from memory or an input/output device onto the data bus.

Write  $(\overline{WR})$ : When low, indicates that the data on the 8080A data bus are stable for WRITE memory or output operation.

Hold Acknowledge (HLDA): When high, indicates that the 8080A data and address buses will go to their high impedance state. When in the data bus read mode, DBIN input in the high state, a high HLDA input will latch the data bus information into the driver circuits and gate off the applicable control signal I/OR, MEMR, or INTA (return to the output high state).

**Bus Enable (BUSEN):** Asynchronous DMA input to the internal gating array. When low, normal operation of the internal bidirectional bus driver and gating array occurs. When high, the bus driver and gating array are driven to their high impedance state.

$V_{CC}$  Supply: +5V.

Ground: 0V reference.

#### OUTPUT SIGNALS

Memory Read (MEMR): When low, signals data to be loaded in from memory. The MEMR signal is generated by strobing in status word 1, 2, or 4. (Refer to status word chart.)

**Memory Write (MEMW):** When low, signals data to be stored in memory. The MEMW signal is generated for the DP8238 by strobing in status word 3 or 5. (Refer to status word chart.) For the DP8228, the MEMW signal is generated by gating a low-level WR input with the strobed in status word 3 or 5.

**Input/Output Read** ( $\overline{I/OR}$ ): When low, signals data to be loaded in from an addressed input/output device. The  $\overline{I/OR}$  signal is generated by strobing in status word 6.

Input/Output Write ( $\overline{I/OW}$ ): When low, signals data to be transferred to an addressed input/output device. The  $\overline{I/OW}$  signal for the DP8238 is generated by strobing in status word 7. For the DP8238 the  $\overline{I/OW}$  signal is generated by gating in a low-level  $\overline{WR}$  input with the strobed in status word 7.

Interrupt Acknowledge (INTA): When low, indicates that an interrupt has been acknowledged by the 8080A microprocessor. The INTA signal is generated by strobing in staus word 8 or 10.

Signal Level Interrupt (RST 7): When the  $\overline{\text{INTA}}$  output is tied to 12V through a 1 k $\Omega$  resistor, strobing in status word 8 or 10 will cause the CPU data bus outputs, when active, to go to the high state.

#### **INPUT/OUTPUT SIGNALS**

### Functional Pin Definitions (Continued)

tion between the CPU, memory, and input/output devices for instructions and data transfers. A status word (which describes the current machine cycle) is also outputted on this data bus during the first microcycle of each machine cycle (SYNC = logic 1).

**System Data (DB<sub>7</sub>–DB<sub>0</sub>) Bus:** This bus comprises eight TRI-STATE input/output lines that connect to the memory and input/output components of the system. The internal bidirectional bus driver isolates the DB<sub>7</sub>–DB<sub>0</sub> Data Bus from the D<sub>7</sub>–D<sub>0</sub> Data Bus.

| Status Word Chart                |        |                |                |                |                |                |                |                |                |         |

|----------------------------------|--------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---------|

| Machine Cycle                    | Status | Data Bus Bit   |                |                |                |                |                |                |                | Control |

| Machine Cycle                    | Word   | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | Signal  |

| Instruction Fetch                | 1      | 1              | 0              | 1              | 0              | 0              | 0              | 1              | 0              | MEMR    |

| Memory Read                      | 2      | 1              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | MEMR    |

| Memory Write                     | 3      | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | MEMW    |

| Stack Read                       | 4      | 1              | 0              | 0              | 0              | 0              | 1              | 1              | 0              | MEMR    |

| Stack Write                      | 5      | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              | MEMW    |

| Input Read                       | 6      | 0              | 1              | 0              | 0              | 0              | 0              | 1              | 0              | I/OR    |

| Output Write                     | 7      | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 0              | I/OW    |

| Interrupt Acknowledge            | 8      | 0              | 0              | 1              | 0              | 0              | 0              | 1              | 1              | INTA    |

| Halt Acknowledge                 | 9      | 1              | 0              | 0              | 0              | 1              | 0              | 1              | 0              | (none)  |

| Interrupt Acknowledge While Halt | 10     | 0              | 0              | 1              | 0              | 1              | 0              | 1              | 1              | INTA    |

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.